## Res Electricae Magdeburgenses

MAgdeburger FOrum zur Elektrotechnik

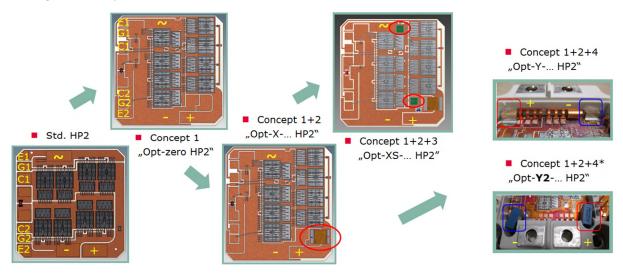

This work serves as a contribution to improve the EMI performance of electrical drive systems in vehicles; the focus is on the power semiconductor module for automotive application.

For a better and deeper understanding of the conducted EMI source, the conducted EMI mechanisms and effects in the drive system are investigated through simulations as well as measurements with special consideration of power modules: The influence of the diode recovery effects on the EMI performance is quantitatively analyzed with different load currents, as well as with different types of diodes, e.g. SiC Schottky barrier diode. Through the simulation, the influence coming from the power module to the system is clarified; the importance of different factors inside and outside of the power module regarding EMI performance are therefore evaluated. To validate the simulation results, the setup and test bench for a conventional EMI measurement for the typical automotive application are presented. Through the measurement results it is proven that the simulation models are usable under certain boundary conditions for future power module designs with regard to the EMI prediction.

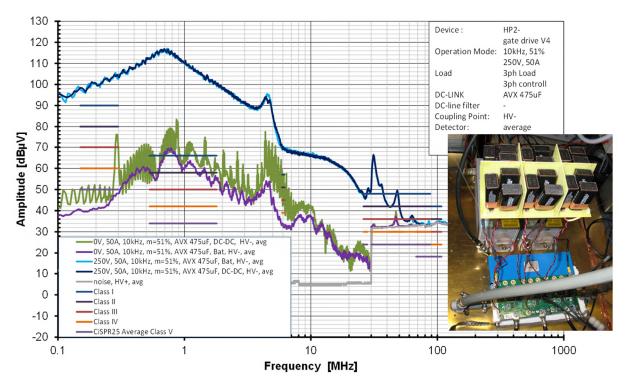

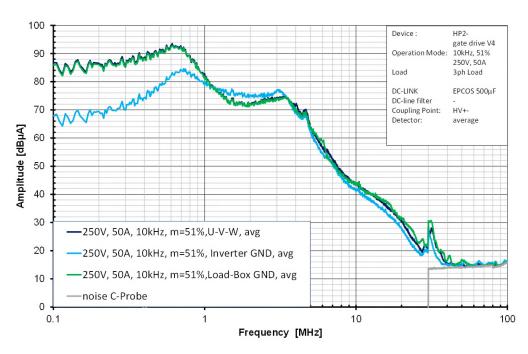

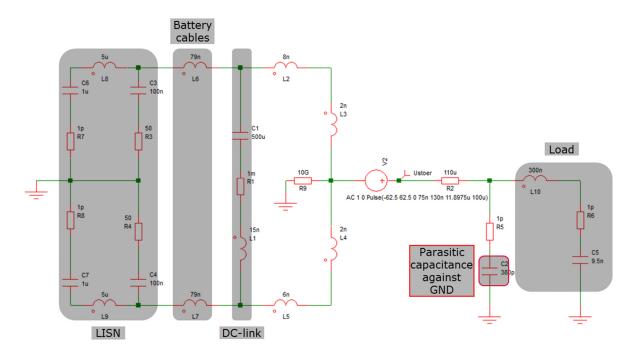

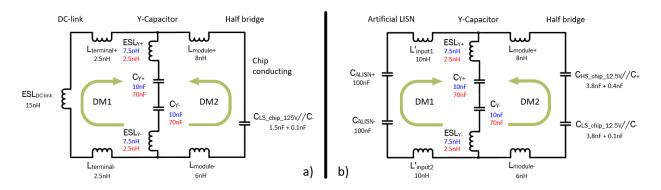

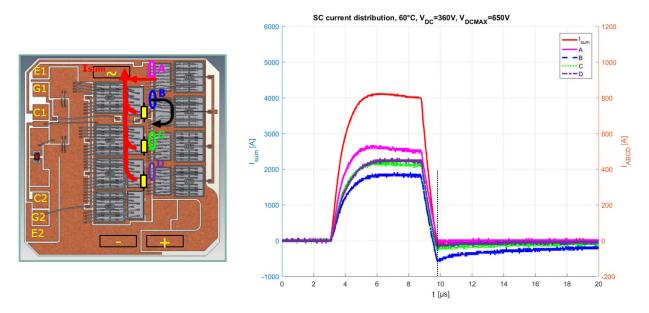

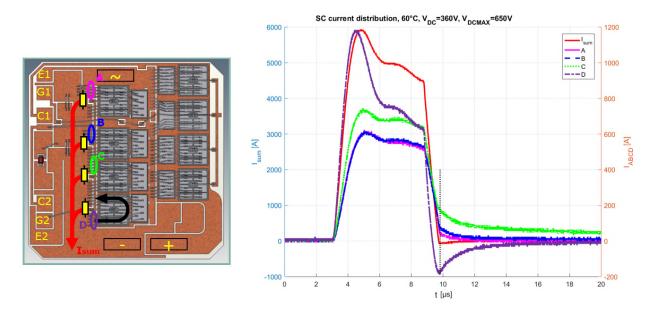

Based on the understanding and the conclusions from the simulation and measurement results, concrete EMI optimization concepts for an inherently low-interference power module are developed and realized. The EMI performance as well as the feasibility of the sample modules are compared and evaluated under different criteria from the power module manufacturer's point of view. Besides, the dynamic and short-circuit performances of the sample modules, regarding to the current distribution on the semiconductor chips, are characterized.

A novel test procedure is introduced in this work, by which it is possible to estimate the conducted EMI performance of power modules without building the whole test setup like in a conventional EMI measurement. This characterization can subsequently be used in the phase of converter development to select a suitable device and evaluate the expected effort to comply with EMI standards.

Yu Liu

Contribution to Improve the

EMI Performance of

Electrical Drive Systems in Vehicles

with Special Consideration of

Power Semiconductor Modules

Yu Liu: Contribution to Improve EMI Performance Power Semiconductor Modules

# Contribution to improve the EMI performance of electrical drive systems in vehicles with special consideration of power semiconductor modules

Der Fakultät für Elektrotechnik und Informationstechnik der Otto-von-Guericke-Universität Magdeburg zur Erlangung des akademischen Grades

Doktoringenieur

(Dr.-Ing.)

am 31.07.2020 vorgelegte Dissertation

von M.Sc. Yu Liu

# Contribution to improve the EMI performance of electrical drive systems in vehicles with special consideration of power semiconductor modules

#### **Dissertation**

zur Erlangung des akademischen Grades

# Doktoringenieur (Dr.-Ing.)

von M.Sc. Yu Liu

geb. am 23.10.1986 in Yunnan, China

genehmigt durch die Fakultät für Elektrotechnik und Informationstechnik der Otto-von-Guericke-Universität Magdeburg

Gutachter: Prof. Dr.-Ing. Andreas Lindemann

Prof. Dr.-Ing. Sibylle Dieckerhoff

Promotionskolloquium am 21. April 2021

### **Res Electricae Magdeburgenses**

Magdeburger Forum zur Elektrotechnik, Jg. 14, Band 82, 2021 http://www.mafo.ovgu.de/

#### **IMPRESSUM**

#### Herausgeber:

- Prof. Dr.-Ing. Andreas Lindemann, Lehrstuhl für Leistungselektronik, Institut für Elektrische Energiesysteme

- Prof. Dr.-Ing. habil. Martin Wolter, Lehrstuhl für Elektrische Netze und Erneuerbare Energie, Institut für Elektrische Energiesysteme

- Prof. Dr. rer. nat. Georg Rose, Lehrstuhl für Medizinische Telematik/Medizintechnik, Institut für Medizintechnik

- Prof. Dr.-Ing. Ralf Vick, Lehrstuhl für Elektromagnetische Verträglichkeit, Institut für Medizintechnik

#### Gründungsherausgeber:

- Prof. Dr. rer. nat. habil. Jürgen Nitsch

- Prof. Dr.-Ing. habil. Zbigniew Antoni Styczynski

alle: Otto-von-Guericke-Universität Magdeburg Postfach 4120, 39016 Magdeburg

#### V. i. S. d. P.:

Dr.-Ing. Yu Liu

Otto-von-Guericke-Universität Magdeburg, Postfach 4120, 39016 Magdeburg

1. Auflage, Magdeburg, Otto-von-Guericke-Universität, 2021

Zugl.: Magdeburg, Univ., Diss., 2021

Auflage: 100

Redaktionsschluss: April 2021

ISSN: 1612-2526

ISBN: 978-3-948749-01-9

DOI: 10.24352/UB.OVGU-2021-055

© Copyright 2021 Yu Liu

Bezug über die Herausgeber

Druck: docupoint GmbH

Otto-von-Guericke-Allee 14, 39179 Barleben

## Acknowledgements

A very special gratitude goes out to BMBF and Infineon Technologies AG for helping and providing the funding for this work. My sincere thanks also goes to Dr.-Ing. Markus Thoben, former head of Infineon automotive high-power module development in Warstein, who provided me an opportunity to join his team as intern, and who gave access to the laboratory and research facilities. Without this precious support it would not be possible to conduct this research.

My deepest gratitude goes foremost to Prof. Dr.-Ing. Andreas Lindemann for the opportunity to carry out this work under his guidance, for his continuous interest and encouragement in my work, and for the long-lasting and fruitful discussions that contributed the success of this thesis.

Special thanks go to Prof. Dr.-Ing. Sibylle Dieckerhoff for her survey of my work; Also to the rest of my thesis committee: Prof. Dr. rer. nat. Christoph Hoeschen and Prof. Dr.-Ing. Ulrich Jumar for their insightful comments.

I would like to express my sincere gratitude to my mentor: Dr.-Ing. Thomas Geinzer for the support of my Ph.D study and related research, for his motivation and immense knowledge.

In particular, I am very much obliged to my colleagues from Infineon Technologies AG in Warstein and in Munich: Yizheng Zhou, Dr.-Ing. Stephan Cordes, Dr.-Ing. Anton Pugatschow, Andreas Groove, Dr.-Ing. Tao Hong and Michael Mankel, for their inspiring scientific discussions, advices and suggestions, which helped me building up the content of this thesis.

I am also grateful to the following funding project partners: Dr.-Ing. habil. Sergey Kochetov, Thomas Smazinka and Dr.-Ing. Stefan Weber, who took part in the study and enabled this research to be possible.

Many thanks to the following colleagues from Infineon Technologies AG in Warstein: Dominik Dauber, Peter Bayer, Patrick Jones and Jennifer Xu for their unfailing support and assistance for the Ph.D work.

Last but not the least, I would like to thank my wife MiPang for supporting me spiritually throughout writing this thesis and my life in general, without which I would have given up this dissertation a long time ago.

Warstein, April 2021

Yu Liu

## **Abstract**

This work serves as a contribution to improve the EMI performance of electrical drive systems in vehicles; the focus is on the power semiconductor module for automotive application.

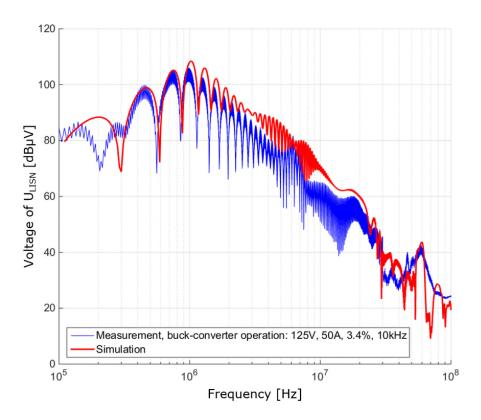

For a better and deeper understanding of the conducted EMI source, the conducted EMI mechanisms and effects in the drive system are investigated through simulations as well as measurements with special consideration of power modules: The influence of the diode recovery effects on the EMI performance is quantitatively analyzed with different load currents, as well as with different types of diodes, e.g. SiC Schottky barrier diode. Through the simulation, the influence coming from the power module to the system is clarified; the importance of different factors inside and outside of the power module regarding EMI performance are therefore evaluated. To validate the simulation results, the setup and test bench for a conventional EMI measurement for the typical automotive application are presented. Through the measurement results it is proven that the simulation models are usable under certain boundary conditions for future power module designs with regard to the EMI prediction.

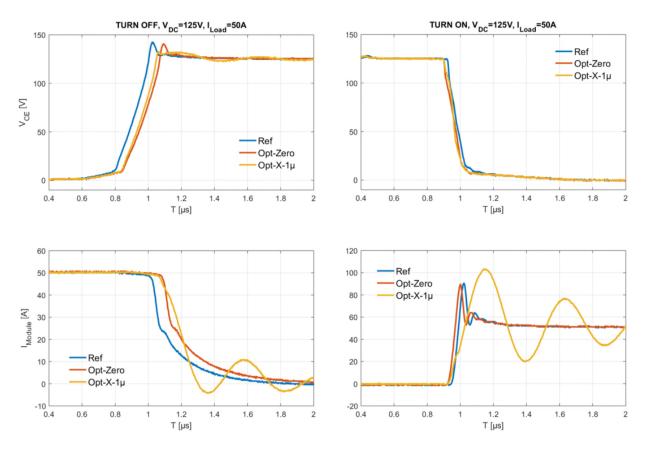

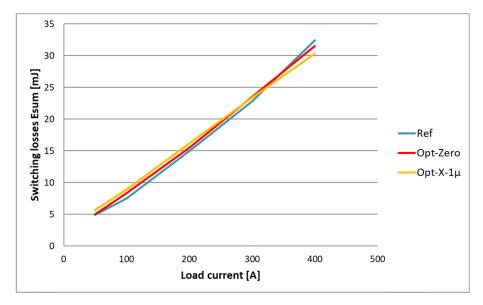

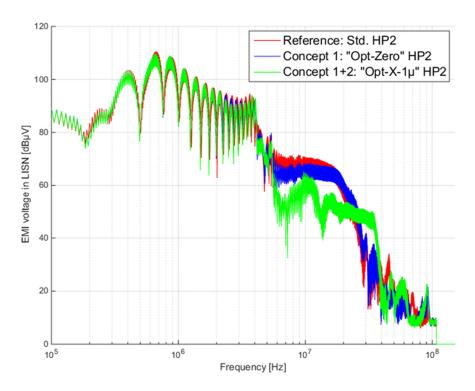

Based on the understanding and the conclusions from the simulation and measurement results, concrete EMI optimization concepts for an inherently low-interference power module are developed and realized. The EMI performance as well as the feasibility of the sample modules are compared and evaluated under different criteria from the power module manufacturer's point of view. Besides, the dynamic and short-circuit performances of the sample modules, regarding to the current distribution on the semiconductor chips, are characterized.

A novel test procedure is introduced in this work, by which it is possible to estimate the conducted EMI performance of power modules without building the whole test setup like in a conventional EMI measurement. This characterization can subsequently be used in the phase of converter development to select a suitable device and evaluate the expected effort to comply with EMI standards.

#### Keywords

EMI, Power module, Automotive application, FFT, Diode reverse recovery, SiC diode, dv/dt, Time-domain simulation, Passive measurement, HF-modeling, Resonance frequency, DCB layout, Parasitic capacitance, Snubber, X-capacitor, Y-capacitor

# Kurzfassung

Diese Arbeit dient als Beitrag zur Verbesserung des EMV-Verhaltens elektrischer Antriebssysteme in Fahrzeugen, wobei der Fokus auf dem Leistungshalbleitermodul für die Automobilanwendung liegt.

Für ein besseres und tieferes Verständnis der Quelle von leitungsgebundenen Störungen werden die EMV-Mechanismen und -Effekte im Zusammenhang mit dem Leistungsmodul im Antriebssystem durch Simulationen und Messungen untersucht. Der Einfluss der Diode Reverse Recovery Effekte auf das EMV-Verhalten wird quantitativ mit verschiedenen Lastströmen sowie mit verschiedenen Diodentypen, wie z.B. SiC-Schottky-Dioden, analysiert. Durch Simulationen wird der Einfluss des Leistungsmoduls auf das System untersucht; auf dieser Basis wird die Bedeutung verschiedener Faktoren innerhalb und außerhalb des Leistungsmoduls für das EMV-Verhalten bewertet. Zur Validierung der Simulationsergebnisse wird der Messaufbau für eine konventionelle EMV-Messung für die Automobilanwendung vorgestellt. Die Messergebnisse belegen, dass die Simulationsmodelle unter bestimmten Randbedingungen für zukünftige Leistungsmodulkonstruktionen zur EMV-Vorhersage verwendbar sind.

Basierend auf dem Verständnis, wie es aus den Simulationen und Messergebnissen hergeleitet wurde, werden konkrete Optimierungskonzepte für ein inhärent störungsarmes Leistungsmodul entwickelt und realisiert. Dessen EMV-Verhalten sowie der Aufwand des Musterbaus aus Sicht des Leistungsmodulherstellers werden anhand verschiedenen Kriterien verglichen und bewertet. Außerdem wird das dynamische und Kurzschlussverhalten der Prototypen einschließlich der Stromverteilung zwischen den Halbleiterchips charakterisiert.

In dieser Arbeit wird ein neuartiges Testverfahren vorgestellt, mit dem es möglich ist, das leitungsgebundene EMV-Verhalten von Leistungsmodulen abzuschätzen, ohne den gesamten Testaufbau wie bei einer konventionellen EMV-Messung zu erstellen. Diese Charakterisierung kann anschließend in der Phase der Inverterentwicklung verwendet werden, um ein geeignetes Modul auszuwählen und den erwarteten Aufwand zur Einhaltung der EMV Standards zu bewerten.

# List of publications

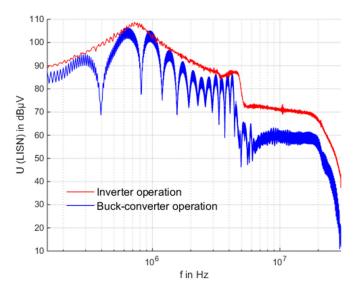

- i) Y. LIU, S. CORDES, T. GEINZER, J. THIELE, M. THOBEN and A. LINDEMANN: Comparison of EMI behavior in inverter and buck-converter operation of power modules by considering the diode reverse recovery effects. CIPS 2016, 9th International Conference on Integrated Power Electronics Systems, Nürnberg, 2016.

- ii) Y. LIU, S. KOCHETOV, T. SMAZINKA and A. LINDEMANN: Characterizing the Conducted EMI Performance of a Power Module through Passive Measurement. PCIM Europe 2017, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nürnberg, 2017.

- iii) Y. LIU, T. GEINZER, S. CORDES and J. THIELE: Inhärent Störungsarme Leistungselektronik InSeL: Teilvorhaben: Infineon Technologies AG: EMV-gerechtes Design von Leistungselektronikmodulen für Automotive-Anwendungen: Schlussbericht InSeL: Berichtszeitraum: 01.01.2014 bis 31.12.2016. TIB/BMBF-Bibliothek, Infineon Technologies AG, München, 2017.

# **Contents**

| Acknowledgements                                                                       | i          |

|----------------------------------------------------------------------------------------|------------|

| Abstract                                                                               | iii        |

| Kurzfassung                                                                            | iv         |

| List of publications                                                                   | v          |

| Contents                                                                               | I          |

| List of Acronyms                                                                       | III        |

| List of Symbols                                                                        | V          |

| 1. Introduction                                                                        | 1 -        |

| 2. State of the art                                                                    | 5 -        |

| 2.1. Conducted electromagnetic interference                                            | 5 -        |

| 2.1.1. Origin of conducted EMI                                                         |            |

| 2.1.2. Spreading and coupling mechanisms of conducted EMI                              |            |

| 2.1.3. EMI standards for industrial and automotive applications                        | 12 -       |

| 2.2. Switching behavior of semiconductors and its characterization                     | 17 -       |

| 2.2.1. IGBTs and diodes in power modules                                               | 17 -       |

| 2.2.2. Characterizing the switching behavior through double-pulse measurements         | 20 -       |

| 3. Investigations about the EMI source                                                 | 23 -       |

| 3.1. FFT analysis of unideal switching edge                                            | 23 -       |

| 3.2. EMI differences in buck-converter and inverter operations by considering the DI   | RR effects |

|                                                                                        |            |

| 3.2.1. Effect of DRR on switching edges                                                |            |

| 3.2.2. Inconstant $d\mathbf{v}/d\mathbf{t}$ because of variable load currents          | 34 -       |

| 3.3. EMI performance of the SiC diode without DRR effect                               | 36 -       |

| 4. Analysis of power module's EMI performance on system level                          | 41 -       |

| 4.1. Conventional EMI measurement methods for automotive drive system                  | 41 -       |

| 4.1.1. Measurement approaches with LISN                                                | 42 -       |

| 4.1.2. Measurement approaches with current sensor                                      | 44 -       |

| 4.2. Time-domain simulation models for conducted EMI analysis                          | 46 -       |

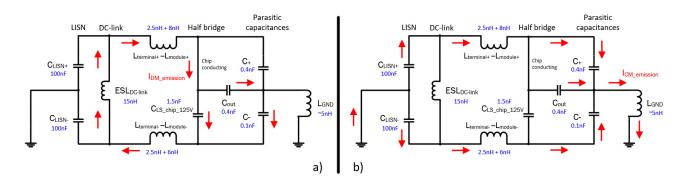

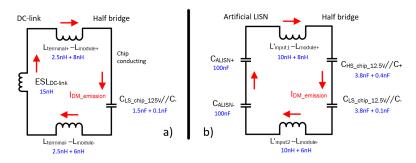

| 4.2.1. Simplified time-domain simulation with separated common- and differential-modes |            |

| 4.2.2. Refined time-domain simulation for conducted EMI and its verification           |            |

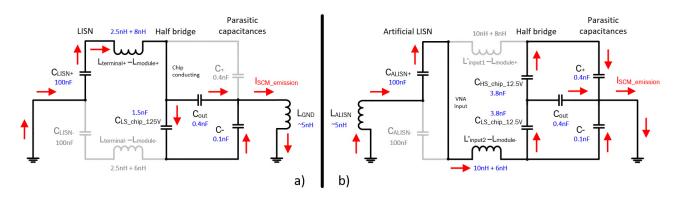

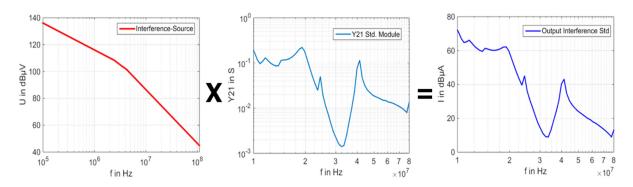

| 5. A new EMI measurement method for automotive power modules                    | 55 -         |

|---------------------------------------------------------------------------------|--------------|

| 5.1. Parameterization and high frequency modeling of the power module           |              |

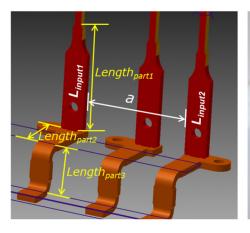

| 5.1.1. Module Pin inductances                                                   |              |

| 5.1.2. Chip and DCB parasitic capacitances                                      | 58 -         |

| 5.2. Mechanism and setup of the passive measurement                             | 59 -         |

| 5.3. Verification of the passive measurement results                            | 65 -         |

| 6. EMI optimization in automotive application with special consideration of p   | power module |

|                                                                                 | 69 -         |

| 6.1. EMI-Optimization of the module DCB layout                                  | 71 -         |

| 6.1.1. Concept, explanation and realization on an automotive power module       | 72 -         |

| 6.1.2. Characterization of the realized automotive power module                 | 75 -         |

| 6.2. Reducing the DM interference by integrating X-Capacitors into the power mo | odule 81 -   |

| 6.3. Reducing the CM interference by integrating Y-capacitors into the power mo | dule 90 -    |

| 6.4. Evaluation of the EMI optimization concepts                                | 94 -         |

| 7. Summary and future prospects                                                 | 97 -         |

| Bibliography                                                                    | 101 -        |

| List of Figures                                                                 | 109 -        |

| List of Tables                                                                  | 113 -        |

| Declaration of Honor                                                            | 115 -        |

# **List of Acronyms**

AC Auxiliary Collector / Alternating Current

AE Auxiliary Emitter

AMB Active Metal Brazed

CENELEC European Committee for Electrotechnical Standardization

CISPR International Special Committee on Radio Interference

CM Common Mode

DC Direct Current

DCB Direct Copper Bonded

DM Differential Mode

DRR Diode Reverse Recovery

EMI Electromagnetic Interference

ESL Equivalent Series Inductivity

ESR Equivalent Series Resistance

FCC Federal Communications Commission

FFT Fast Fourier Transform

HF High Frequency (3 - 30 MHz)

HS High Side

HV High Voltage in automotive application (less than 1 kV, normally 400 V)

IEC International Electrotechnical Commission

ISO International Organization for Standardization

LF Low Frequency (30 - 300 kHz)

LISN Line Impedance Stabilization Network

LS Low Side

LV Low Voltage

MF Medium Frequency (300 - 3000 kHz)

PDS Power Drive System

PWM Pulse Width Modulation

RBSOA Reverse Bias Safe Operating Area

RMS Root Mean Square

SCM Similar Common Mode

VHF Very High Frequency (30 - 300 MHz)

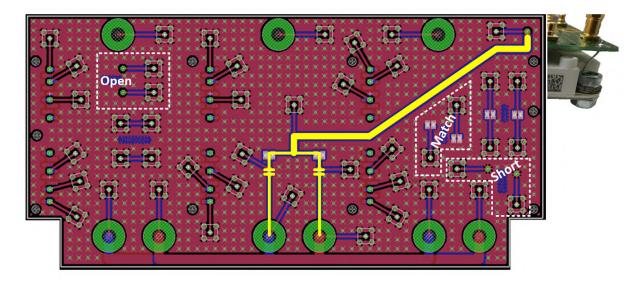

VNA Vector Network Analyzer

# **List of Symbols**

A Amplitude of the trapezoidal pulse

a Distance between two wires

Parasitic capacitances of the positive and negative power module

potential

C<sub>1,2</sub> Capacitors in LISN

Collector-emitter capacitance of the IGBT

$C_{Diode}$  Diode capacitance

C<sub>GC</sub> Gate-collector capacitance of the IGBT

C<sub>GE</sub> Gate-emitter capacitance of the IGBT

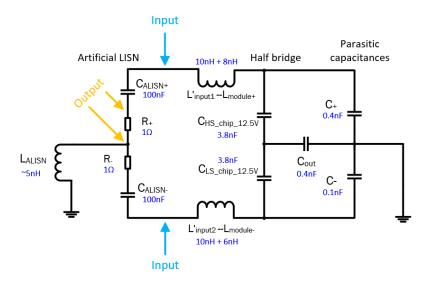

C<sub>HS\_chip</sub> Chip capacitance of the half-bridge high-side

$C_K$  Coupling capacitance

$C_{LS\ chip}$  Chip capacitance of the half-bridge low-side

Cout Output capacitance of the power module's AC knot

C<sub>S</sub> Cable shields capacitance

$C_{W,g}$  E-machine windings capacitance

E<sub>off</sub> Switching loss by IGBT turn-off

E<sub>on</sub> Switching loss by IGBT turn-on

E<sub>sum</sub> Sum of turn-on loss and turn-off loss

F Fall time of the trapezoidal pules

F' Normalized Fall time of the trapezoidal pules

$f_{k1,2,3}$  Knee frequencies of the spectrum

*f*<sub>switch</sub> Switching frequency

*I*<sub>C</sub> Current flowing in IGBT

*I<sub>CES</sub>* Collector-emitter cut-off current

*I<sub>CM1,2</sub>* Leakage currents

*I<sub>CN</sub>* Implemented collector current of the power module

*I<sub>DC,buck</sub>* Current in the buck-converter operation mode

*I<sub>F</sub>* Current flowing in diode

*I*<sub>Load</sub> Load current

*I<sub>rec</sub>* Reverse recovery current of the diode

*I<sub>RMS,inv</sub>* RMS current in the inverter operation mode

I<sub>RMS\_Load</sub> RMS value of the load current

*k* Multiples of the fundamental frequency

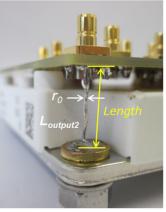

Length of the wire

$L_{t}$ . Stray inductances of the positive and negative power module potential

L<sub>1</sub> Inductors in LISN

*L*<sub>input,output</sub> Stray inductances of the power module pins

$L_p$  Inductance per length

L<sub>s</sub> Stray inductance of cable or bond wire

M Average duration of the trapezoidal pulse

*m* Modulation degree of the PWM

M' Normalized average duration of the trapezoidal pulse

R Rise time of the trapezoidal pulse

R' Normalized rise time of the trapezoidal pulse

$r_0$  Radius of the wire

R<sub>1,2</sub> Resistors in LISN

T Period of the trapezoidal pules

$T_{f0}$  Fundamental period of the sinusoidal current

*t*<sub>fall</sub> Fall time of the switching edge

*t<sub>p</sub>* Duration of the plateau in trapezoidal pules

$T_{pulse}$  Defined time interval

$t_{rise}$  Rise time of the switching edge

$U_{AC}$  Output voltage by each AC knot of the half-bridge

$U_{DC+,-}$  DC-link voltage

$V_{Bat}$  Battery potential of the EV

$V_{CE}$  Collector-emitter voltage of the IGBT

$V_F$  Forward voltage drop on the diode

$V_R$  Reverse voltage drop on the diode

$V_{GE}$  Gate-Emitter voltage of the IGBT

V<sub>GEth</sub> Threshold voltage of the IGBT

*V<sub>ind</sub>* Induced voltage

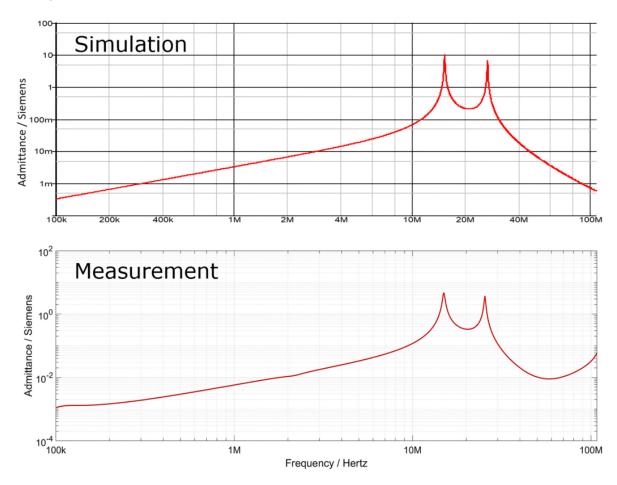

Y Admittance curve from the passive measurement

Impedance defined connecting the heat-sink and the electric circuit of the

power module

$\mathcal{E}_r$  Relative permittivity

$\mu$  Permeability

## 1. Introduction

Power electronics is a key element for the low-loss conversion of electrical energy. In an electrical drive system, the motor speed can be controlled by using an inverter. In an energy conversion system, e.g., the voltage level can be adjusted by using a DC/DC converter. However, in a vehicles' drive system, to integrate the inverter, the DC/DC converter and the charging equipment etc. into extremely limited space, it is very difficult to comply with the EMI limits and keep the EMI immunity, since during the signal transmission, the internal devices in the vehicle can interfere with each other. In order to meet all the requirements for future use in electrified drives, from the economic and space view, an EMC-optimized design of the submodules in the system, the use of targeted shielding / filtering measures as well as optimal PCB layouts, are absolutely necessary [5][80].

The main motivation of this dissertation is to research and optimize the main source of the EMI: -the power module. In this work, scientific concepts, simulation and measurement methods for designing the novel, low-interference power modules are developed and implemented. Some demonstrators are realized, characterized and then evaluated with regard to their EMI potential as well as other criteria. A newly developed measurement method is also intended to enable the power module manufacturer to pre-evaluate the products' EMI behavior without obtaining the concrete system information from the vehicle OEMs.

Generally, this dissertation is organized as follows:

Chapter 2 gives the state of the art of the conducted EMI and its main source, the power semiconductor module. The origin, spreading and coupling mechanisms of the conducted EMI are explained; the relevant standards that are currently used in industrial and automotive applications are summarized and compared. Besides, the relevant basic knowledge about the dynamic performance of the semiconductors within the power module is indroduced; the recommended manner of the dynamic characterization of the power modules is also presented.

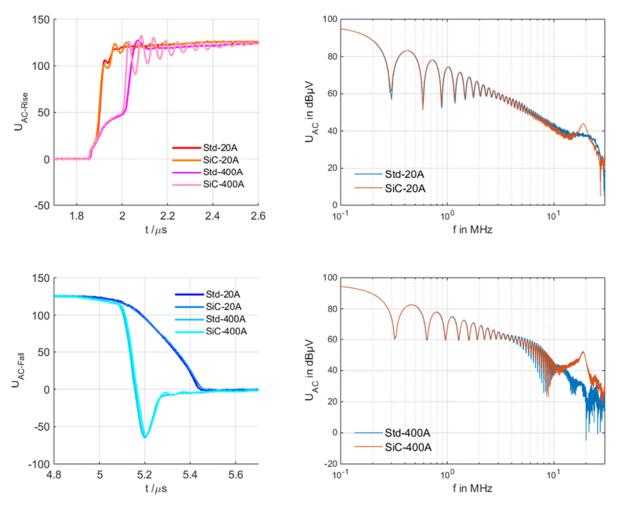

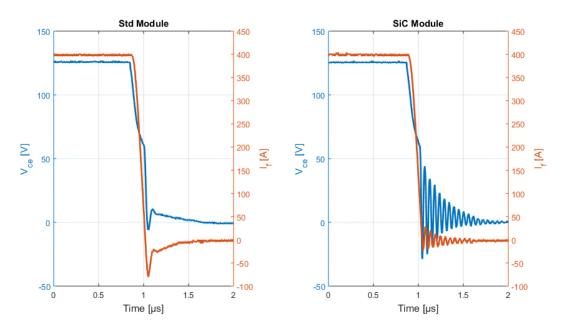

Chapter 3 investigates some effects regarding the source of the conducted EMI, i.e., the switching edges of the semiconductor with large dv/dt. The content mainly includes: the spectrum analysis of the unideal switching edge which contains a plateau, the discussion of the inconstant dv/dt of the switching edges that are caused by the DRR effect as well as the variable load current, the expectation and validation of the switching edges' dv/dt that are produced by a SiC diode without DRR effect. According to these investigations, some conclusions are drawn regarding the EMI performance of the power converter's different operation modes.

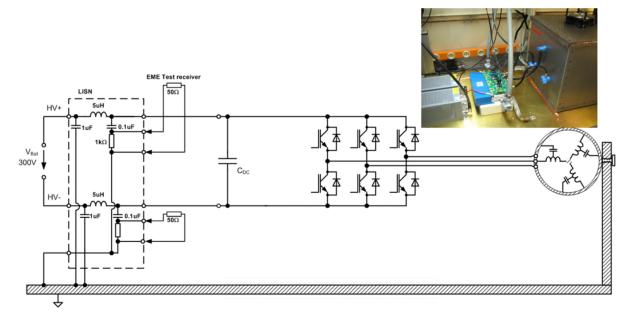

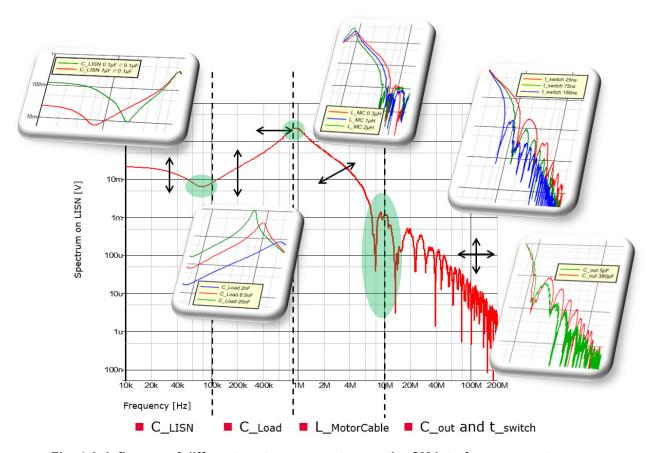

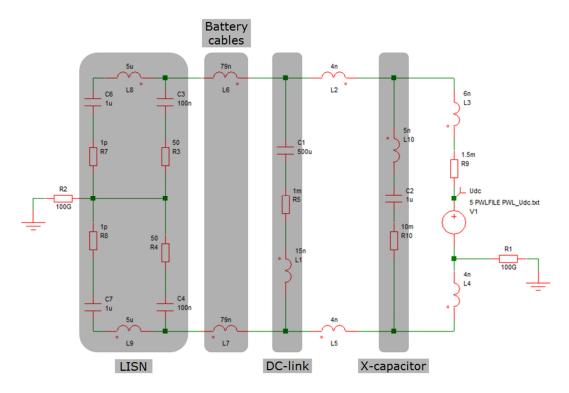

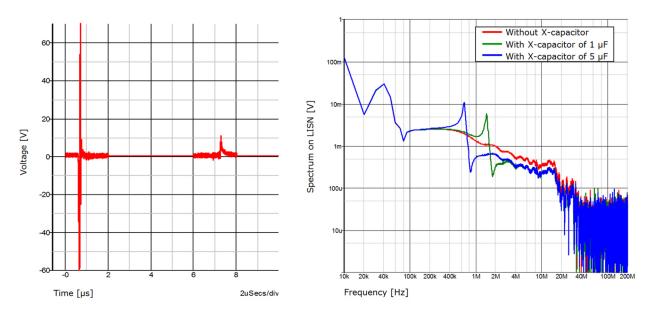

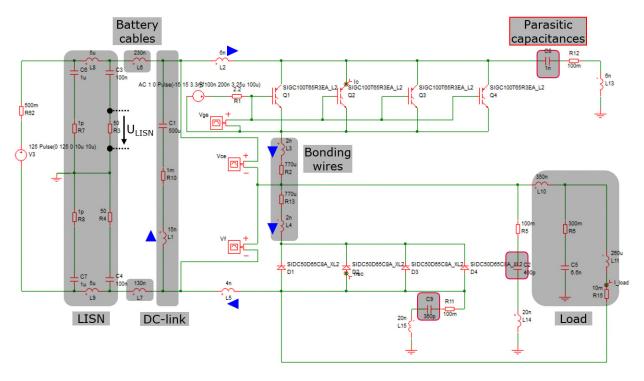

In chapter 4, based on the understanding of the effects of the EMI source, the discussion is extended into the level of the drive system in the automotive application. For the later improvement of the power module's EMI performance, the simplified time-domain simulation models on system-level are built up. Through the simulation, the influences coming from the power module to the system can be better clarified; the importance of different factors inside / outside of the power module can be therefore evaluated. To validate the simulation results, the

setup and test bench of the conventional EMI measurement for a typical automotive application are presented. The measurement approaches used in this dissertation are explained and discussed.

From the power module manufacturer's point of view, performing a basic EMI qualification of its products independent on the system makes sense. In chapter 5, based on some existing research results, the usage of a new test procedure makes it possible to estimate the conducted EMI performance of the power module without building the whole test setup like in a conventional EMI measurement. This characterization can subsequently be used in the phase of converter development to select a suitable device and evaluate the expected effort to comply with EMI standards.

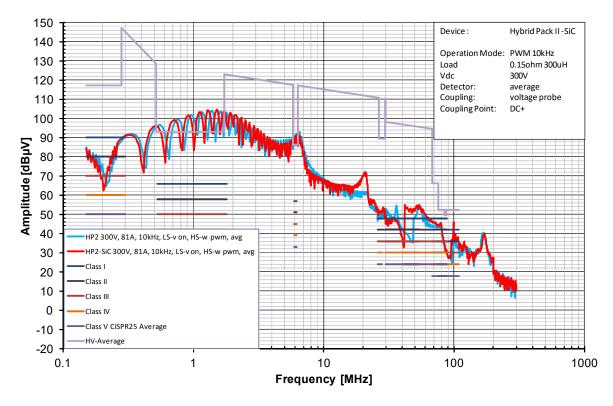

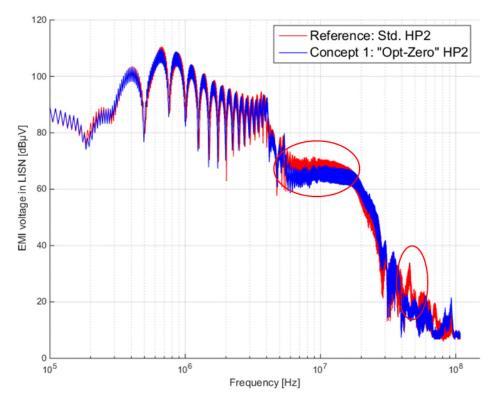

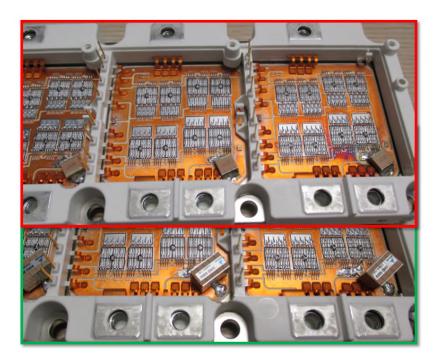

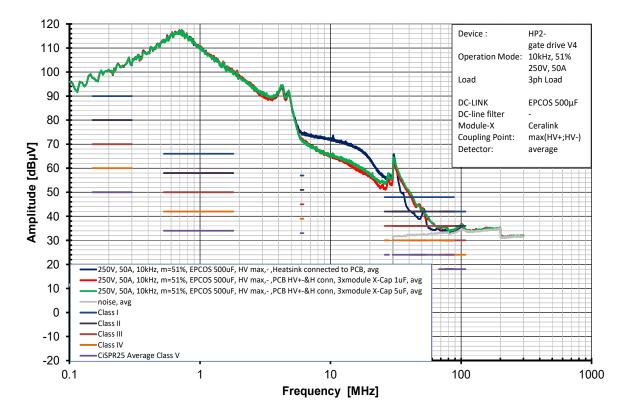

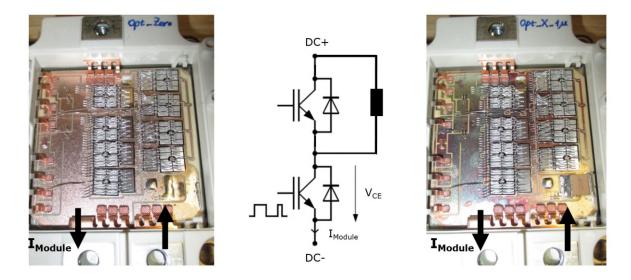

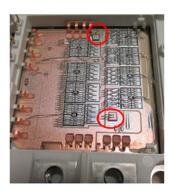

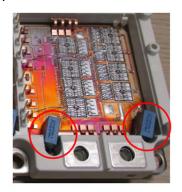

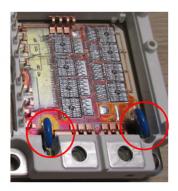

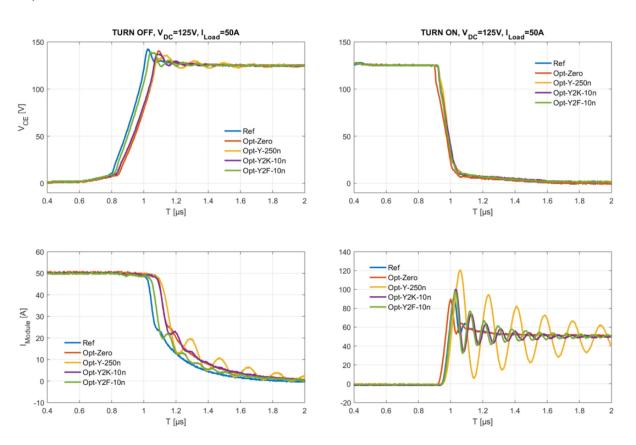

In chapter 6, as the main motivation of this dissertation, the research for the EMI optimization of the power module is described. Based on the researched power modules for industrial applications by Domurat-Linde and Domes, the EMI optimization concepts are extended to cover the power modules for automotive application. Using the measurement and simulation results in chapter 3 and 4, further ideas and solutions for the inherent low-interference power module are developed and realized in Infineon®'s HybridPACK™ 2 module package for EV application. The EMI performance as well as the feasibility of the sample modules are compared and evaluated under different criteria from the power module manufacturer's point of view. Besides, the dynamic and short-circuit performances of the sample modules are characterized, in order to specially investigate the new current distribution on the semiconductor chips due to the changed DCB layout structure and the switching losses because of the insertion of the external capacitors.

Chapter 7 closes this dissertation with some conclusions and future work.

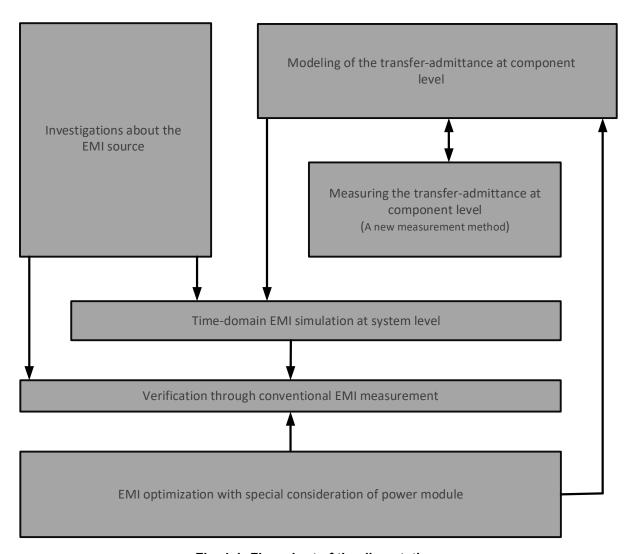

From the flow chart's point of view, the methodology and procedure of this dissertation are mainly presented by 5 parts as shown in Fig. 1-1:

- Investigations about the EMI source

In this part some interesting effects regarding the conducted EMI source are investigated (referring chapter 3).

- Modeling / measuring the transfer-admittance at component level

In this part the system components in the drive system are modeled or measured. Since the conducted EMI are transferred by them, the natural frequency of these components can magnify the EMI in some frequency ranges (referring chapter 4 and 5).

- Time-domain simulation on system level For this part, the EMI source and its transfer paths (admittance) are combined to establish a simplified drive system in the simulation, so that the influences coming from the power module to the system can be better clarified; the importance of different factors inside / outside of the power module can therefore be evaluated. This lays the foundation for how the EMI elements shall be considered in the optimization of power modules for the next part.

- EMI optimization with special consideration of power module

Based on the understanding of the effects as well as the gained knowledge from the above parts, the conducted EMI optimization on the power module can finally be implemented in this part.

- Verification of the results by conventional EMI measurements

The research results in all above parts are respectively verified through the conventional EMI measurements.

Fig. 1-1: Flow chart of the dissertation

## 2. State of the art

## 2.1. Conducted electromagnetic interference

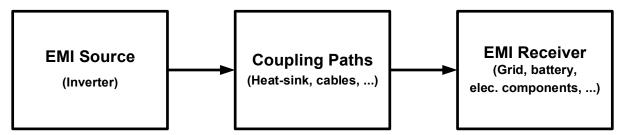

According to the Official Journal of the European Union, the EMC is defined as "the ability of equipment to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances to other equipment in that environment" [75]. In other words, the equipment must not cause interference to other equipment in its surroundings nor to itself and must not be susceptible to emissions from other systems. Consequently, EMC is concerned with the generation, transmission and reception of electromagnetic disturbances [76]. In general, the electromagnetic interference energy, commonly called the EMI, is generated by an interference source, and then transmitted through a coupling path into a receiver.

Fig. 2-1: Basical decomposition of the EMI issue

The simplified diagram in Fig. 2-1 illustrates this described situation: The power electronics are a source of electromagnetic interference. Because of the fast switching behavior with high voltages and currents, on the one hand, the electromagnetic fields can propagate into the environment; on the other hand, high-frequency currents can be conducted through the wires within the system. Through the coupling paths, the electromagnetic interference can transmit from the source to the receiver. In the case of the power electronics, the grid for power supply in industrial applications, as well as the HV-battery or another electrical component in automotive applications, can be considered as the receiver of the interference. The optimization of the EMI performance can thereby be concluded in three aspects [76]:

- Suppressing the emission at its source,

- Making the coupling path as inefficient as possible,

- Making the reveiver less susceptible to the emission.

In this dissertation, the research is focused on the conducted EMI and its reduction; the radiated EMI is not to be discussed, since nowadays in the automotive and industrial applications, the radiated emissions can usually be defended by using shielding measures. In 2.1.1, the inverter as EMI source of the system will be introduced; in 2.1.2, the coupling paths as well as the interference spreading mechanisms are explained. In 2.1.3, from the EMI

receiver side of view, relevant standards regarding the EMI requirements in automotive and industrial applications are summarized and compared with each other.

### 2.1.1. Origin of conducted EMI

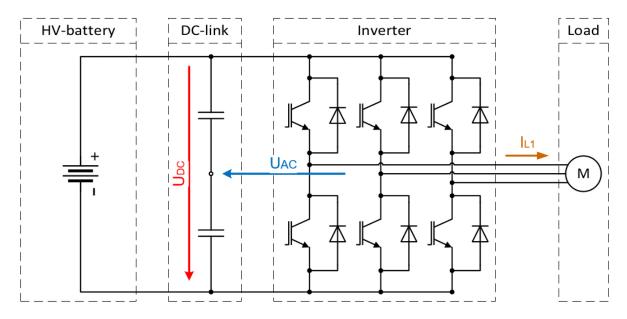

Nowadays, electrical motor drives are widely used in electromechanical energy conversion systems. Working as one of the key components in the drive system, the modern power electronic converters can generate the AC voltage with targeted frequency and amplitude from a DC or AC voltage supply. Depending on the specific application, different types of power converters can be used. One of the most commonly used types in automotive application, consisting of battery, DC-link and inverter, is shown schematically in Fig. 2-2.

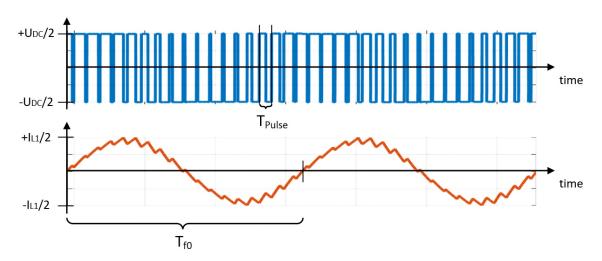

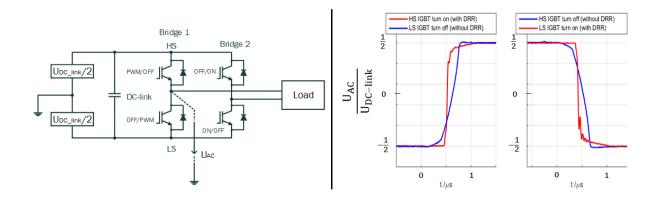

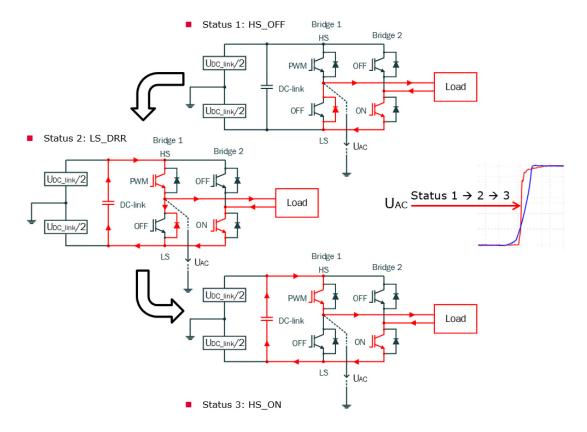

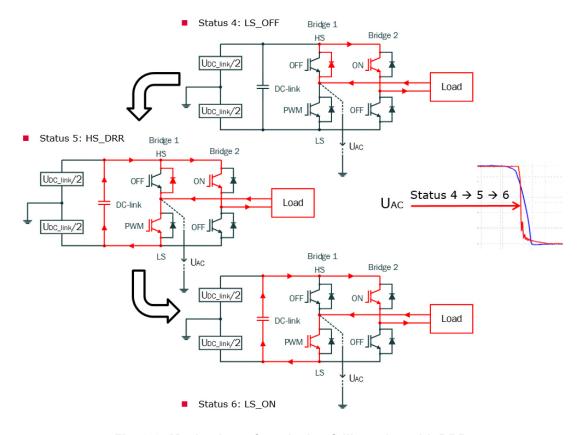

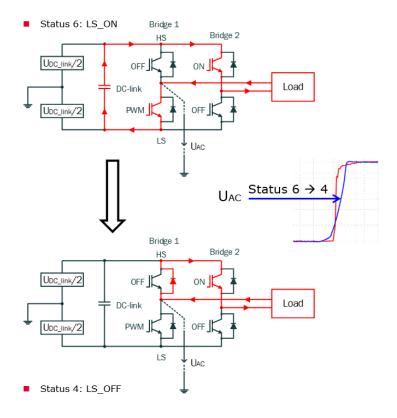

The HV (High Voltage) battery working as input-part of the power converter system can usually be considered as a DC voltage supply. The DC voltage is then smoothed by the DC-link capacitor. The inverter working as output-part of the power converter system consists of three half-bridges, each composed of two IGBTs in high and low side with associated free-wheeling diode. The inverter converts the DC-link voltage into an AC voltage of the targeted frequency, amplitude and phase position, which is required for driving the electrical motor of the load side. For this purpose, the IGBTs are switched on and off via the drive board with the PWM (Pulse Width Modulation) signals, the output voltage  $U_{AC}$  by each AC knot of the inverter switches between the values  $+\,U_{DC}/2$  and  $-\,U_{DC}/2$  to form a series of pulses. Through the chronological changing of the pulse widths, the mean value of  $U_{AC}$  over a defined time interval  $T_{\text{pulse}}$  results in different output voltages whose values lie in between  $+\,U_{DC}/2$  and  $-\,U_{DC}/2$  (see Fig. 2-3 top). Considering that this variable output voltage drops on the motor from the load side, the charging and discharging of the inductive coil will take place alternately along with the IGBT switching. In this way, the sinusoidal load current with the fundimental period of  $T_{f0}$  (see Fig. 2-3 bottom) can be produced in each phase of the inverter.

Within a half-bridge of the inverter, the two IGBTs must not be switched on at the same time. Either the high side or the low side IGBT is switched on by the PWM signal. The current commutation between the IGBT's ON and OFF states always takes place within the half-bridge, combined with the free-wheeling diode of the opposite respectively. Since the high side and the low side switch from different half-bridges perform analogously with each other, it is acceptable to simplify the inverter operation as a buck-converter operation in order to focus on the study of the switching performances [10][11][74]. The feasibility as well as disadvantages of such simplification from the EMI point of view will be further discussed in chapter 3.2.

Fig. 2-2: Schematic diagram of a three-phase power converter consisting with HV-battery, DC-link and inverter

Fig. 2-3: Pulse width modulated signals: output voltage U<sub>AC</sub> (top) and load current (bottom) from one phase of the inverter

Since the inverter is based on PWM techniques with switches characterized by very small switching times, the modulated output voltage signal in the HV drive system for the automotive application (less than 1 kV, normally 400 V) is pulse-shaped. The generated high voltage slew rate dv/dt and high current slew rate di/dt during the switching processes have been established as the main source of EMI in electrical applications [1][2][5][9][11][17][48][50][51].

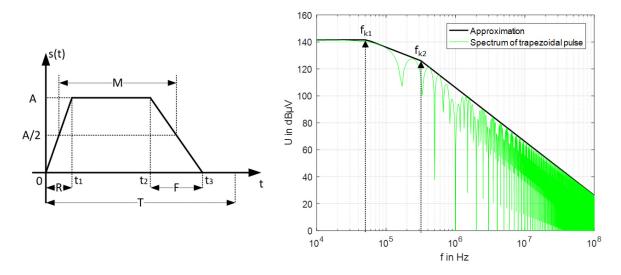

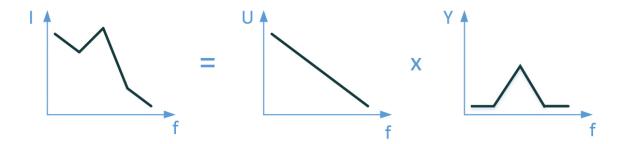

For a better understanding of the EMI source, the pulse that is generated by the inverter can be approached by a trapezoidal curve in time-domain; its spectrum can be calculated analytically for the approximation. This result can be used as interference voltage source in a frequency-domain circuit simulation [1][5][53]. For example, to build up an interference source of the simulation model in [1], the output voltage of the AC knot during the IGBT switching has been measured, then approximated by a trapezoidal pulse overlaid with an oscillation of 33 MHz. After that it has been translated into a spectrum of 3 MHz to 300 MHz and used in the frequency-domain model which consists of a voltage source and other passive RLC components. The advantage of the analytical calculation of the spectrum is that the equation

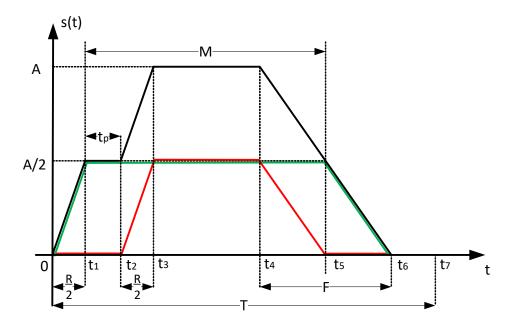

can reveal the relationships between the parameters of the approached pulse in time-domain and the resulting spectrum in frequency-domain. It is thereby possible to find out how the spectrum is generated and which parts of the time-domain signal make a decisive contribution. Generally, the pulse in trapezoidal shape with defined parameters: a rise time R, a fall time F, the pulse's amplitude A and the average duration M (Fig. 2-4 left), is used as a typical object for the analytical calculation [1][2][5][51]. The average duration M means the time during which the signal s(t) is larger than half of its amplitude. For the calculation the parameters are normalized and marked with an apostrophe: t' = t/T, M' = M/T, R' = R/T and F' = F/T. The total trapezoidal pulse can be described by three functions defined in sections [1]:

$$s_{1}(t') = \frac{A}{R'}t' \qquad ; 0 \le t' < t'_{1} \qquad ; t'_{1} = R'$$

$$s_{2}(t') = A \qquad ; t'_{1} \le t' < t'_{2} \qquad ; t'_{2} = \frac{R'}{2} + M' - \frac{F'}{2}$$

$$s_{3}(t') = \frac{A}{F'}\left(M' + \frac{R'}{2} + \frac{F'}{2} - t'\right) \qquad ; t'_{2} \le t' \le t'_{3} \qquad ; t'_{3} = \frac{R'}{2} + M' + \frac{F'}{2}$$

$$(2-1)$$

By considering that the pulse will repeat uniformly, the continuous Fourier transformation can be carried out, when the period T of the time-domain trapezoidal signal s(t) is taken into account:

$$\frac{S(\omega')}{2} = \int_{0}^{R'} \frac{A}{R'} \cdot t' \cdot e^{-j\omega' \cdot t'} dt' + \int_{R'} A \cdot e^{-j\omega' \cdot t'} dt' + \int_{R'} \frac{\frac{R'}{2} + M' + \frac{F'}{2}}{A' \cdot e^{-j\omega' \cdot t'} dt'} + \int_{R'} \frac{\frac{R'}{2} + M' + \frac{F'}{2}}{A' \cdot e^{-j\omega' \cdot t'} dt'} \left(\frac{A}{F'} \left(M' + \frac{R'}{2} + \frac{F'}{2} - t'\right)\right) \cdot e^{-j\omega' \cdot t'} dt'$$

(2-2)

The equation (2-3) shows the solution of the integral calculus for the signal s(t) in Fig. 2-4 left. The detailed explanation of the mathematic calculation can be found in [1]. As an alternative solution, the purpose can also be fulfilled by programing in MATLAB, using its discrete FFT (Fast Fourier Transformation) and other relevant functions.

$$S(k) = \frac{A}{\pi k} \left[ si(\pi k R') \cdot e^{j\pi k M'} - si(\pi k F') \cdot e^{-j\pi k M'} \right] \quad ; k = fT$$

(2-3)

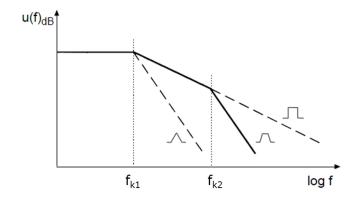

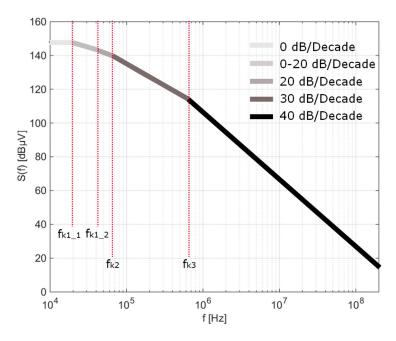

According to the Fourier transformation result from equation (2-3), it is possible to determine the approximation line for the maximum limits of the spectrum. The approximation is nothing more than calculating the envelope curve of the spectrum. According to [5], the approximation line can be divided into different parts and then described by different functions. The dividing points in frequency range are called "knee points". As shown in Fig. 2-4, there are usually at least two knee points  $f_{k1}$  and  $f_{k2}$  visible. The characteristics of the approximation line have been summarized by [5] like this: (translated from German) "Before the frequency reaches the knee point  $f_{k1}$ , the spectrum's amplitude is enveloped by its fundamental's amplitude. The value of  $f_{k1}$  is usually larger than the switching frequency 1/T and reaches its minimum 1/T when the average duration M' is equal to 0.5. For shorter or longer M',  $f_{k1}$  reaches values greater than 1/T. Above of  $f_{k1}$ , the amplitude of the spectrum decreases. In logarithmic terms this means a drop of 20 dB per frequency decade. From the second knee point  $f_{k2}$ , the amplitude is determined by the smoother one of the two switching edges (rise and fall). If the

rise-time R and fall-time F are the same, there will be amplitude dropping of 40 dB per decade here. Above  $f_{\rm k2}$ , the switching edges significantly determine the magnitude of the amplitude, with the steeper edge causing the higher spectrum."

Such envelope approximation includes also the situations like for those pulses by R' = F' = 0 (idealized rectangular pulses) or by  $M' = \frac{R' + F'}{2}$  (unbalanced triangular pulses). The corresponding spectrums of these pulses are schematically presented in Fig. 2-5.

Fig. 2-4: Definition of the trapezoidal pulse in time-domain (left) and its spectrum in frequency-domain in two representations (right)

Fig. 2-5: Amplitude forms for trapezoid, rectangle and triangle pulses

## 2.1.2. Spreading and coupling mechanisms of conducted EMI

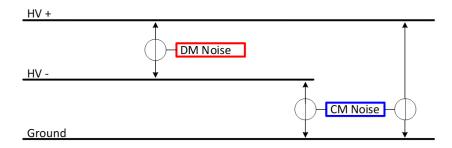

As common sense of the contemporary investigations regarding the EMI, the conducted interferences are usually divided into Differential-Mode (DM) and Common-Mode (CM) noises depending on their origins. The interference modes can convert from one to the other in the power electronics circuits because of unbalance of the system components [1][57][70].

The basic concept of the conducted EMI in DM and CM modes for a single phase are illustrated in Fig. 2-6. By the DM interference, the interference current usually flows within the HV system to build up a closed loop. That means the EMI current transfers along with the load current from one phase to another phase of the system, disturbing the wanted signals by the high frequency noises. Thus, the DM interference is referred to as a symmetrical noise.

By the CM interference, the EMI current transfers though the two (or more) wires of the HV system in the same direction, then returns to its source to close the loop by flowing across the GND. This interference can therefore be measured with the GND as reference. The CM interference is usually generated by potential fluctuation against ground due to the charge and discharge of the parasitic capacitances existing between the HV system and the GND. The CM interference is referred to as asymmetrical noise.

In the electrical applications, both types of interferences are produced simultaneously and are inseparable. According to [68][69][70] and [79], the DM and CM interferences can interact with each other, generating a sort of mixed-mode (MM) interference phenomenon.

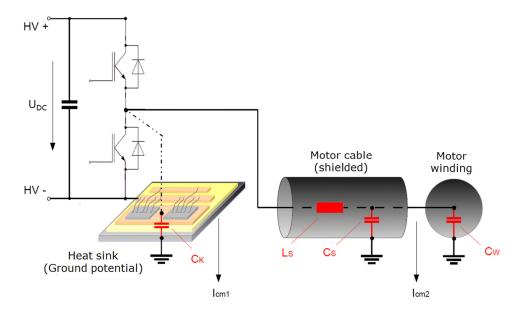

Fig. 2-6: Basic concept of conducted EMI in differential- and common-mode

The switching speed of current silicon (Si) and new silicon carbide (SiC) or gallium nitride (GaN) devices is becoming even higher, enabling the development of even smaller and more efficient inverters. However, due to the faster switching edges, high leakage currents also flow via the coupling capacitance  $C_K$  (see Fig. 2-7) from the HV half-bridge to the inverter heat-sink, via cable shields capacitance  $C_S$  or the winding capacitance  $C_W$  in the electrical machine, which leads to high common-mode EMI.

The research regarding the modeling of the motor cables ( $L_{\rm S}$  and  $C_{\rm S}$ ) can be referenced by literature such as [43][44][45]. For example, to analyze and reduce the EMI generated by the inverter used with a long motor cable, it is necessary to build a satisfactory model of the cable, which should take into account the skin effect [42][46][47] and the proximity effect as well as the dielectric losses. In [43], a finite-element method is used to calculate most of the electrical parameter values of the energy cable model. The proposed unshielded and shielded models were validated in both the frequency and time domains. From the application point of view, while frequency-domain models inherently rely on matrix representations, time-domain models require to build equivalent circuits in the form of numerous cascaded cells to account for propagation phenomena in the cables. Thus, the time-domain simulation is well suited for power converters because semiconductor devices operate in large signal commutation mode, with a strongly nonlinear behavior. However, the frequency domain is best suited for high-frequency modeling, which is required for EMC simulations [44]. The frequency domain model proposed by Marlier, Videt and Idir allows a significant reduction of computation times compared with conventional time-domain simulation, which could allow optimization

procedures at the design stage of a power conversion system. Regarding the shielding issue of the cables, usually a well shielded cable is considered to help relieving the radiated EMI protection, but largely burdens the conducted EMI protection because of the extra shield capacitance C<sub>S</sub> between the HV wires and the grounding. Besides, the termination of the cable shield should also be taken into account, since in [45] it is concluded that external input / output cable-shield termination has the greatest system EMC performance effect of all other design parameters.

The research regarding the modeling of the AC motor (including the motor capacitance  $C_W$ ) can also be referenced by diverse of literature such as [3][4][5][7][8]. In [3], a high frequency model for induction motor based on lumped parameters has been proposed and a measurement procedure to obtain model parameters has been identified; while in [4] and [7], the EMC behavior of induction machines with power ratings from 370 W up to 45 kW is compared and a model library is set up for both frequency- and time-domain. The common-mode as well as differential-mode behaviors of the induction machines are also investigated by using the proposed simulation model and the relevant measurement results. In [8] it is confirmed that, the common-mode impedance of the induction motor can be considered as the capacitance  $C_g$  (in this dissertation designated as  $C_W$  in Fig. 2-7) coupling the winding to ground, which means that the path of common-mode current can be represented by this capacitance.

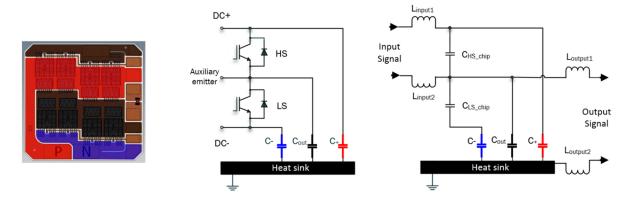

In this dissertation, since the focus of the research is located on the power semiconductor module, most discussions will be carried out regarding the coupling capacitance C<sub>K</sub> (which is later divided into three parts e.g. C+, C- and Cout) in the following chapters, especially in chapter 5 and 6. The coupling capacitance C<sub>κ</sub> mainly comes due to the special construction of the DCB in the power module (see Fig. 2-11), which acts like a parallel plate capacitor with a ceramic layer in between two copper layers. The coupling capacitance can be affected by the construction of the heat-sink which is directly connected to the bottom copper layer of the DCB. Plenty of studies including simulations and measurements are already carried out regarding the influences on the EMC behavior in GHz range when the heat-sink geometry is modified [26][27][28][29], in which the heat-sinks are usually modeled as a solid block. In [30] it is found that the use of one common heat-sink creates the capacitive couplings which cause significant parasitic overshoots and oscillations and in return deteriorates the conducted EMI performance. Instead, the use of separated heat-sinks (between the multi half-bridges of the inverter) significantly reduces the EMI magnitudes especially for the DM noise. In addition, with the combined damping circuits the EMI performance is further improved. In [49] it is found out, in the power transmission system, if the rectifier module is separated from the heat-sink, the leakage current from the inverter module can no longer flow through the parasitic capacitances of the rectifier module back into the DC-link; instead it has to use the "protective conductor" and produces therefore a higher level of conducted EMI. The so called "protective conductor" means the electrical conductor (usually a flat copper strap) used in the active EMI measurement to ground the power module's baseplate as well as the heat-sink, it is designated as "ground strap" in this dissertation and will be further researched and discussed in chapter 4.1.2, 5.2 and 5.3.

Generally, in order to reduce the conducted EMI which is caused by the above mentioned parasitic capacitances  $C_K$ ,  $C_S$  and  $C_W$ , a well-known solution is to build the so-called Y-capacitors (usually combined with ferrite core) from the HV network (HV+, HV-) to the housing

of the power electronic systems [23][24][25]. However, their capacitance values are limited e.g. by the normative (leakage currents, contact protection) or functional requirements (no influence on the insulation monitoring, etc.).

Fig. 2-7: Schematic representation of a commutation cell in power module and the coupling paths of the common-mode EMI (leakage currents I<sub>CM1</sub> and I<sub>CM2</sub>) via heat-sink and motor connection

### 2.1.3. EMI standards for industrial and automotive applications

Since the inverters with power module inside are used for equipment in a wide range of application fields including household appliances, industrial PDS (Power Drive System), automobile and traction system, it is imperative for the designers, as well as for the consumers, that the products comply with the stringent EMC regulations. By doing that, one can make sure that the products will not electrically disturb or being disturbed.

The IEC (International Electrotechnical Commission), which is a division of the ISO (International Organization for Standardization), is the most important international body for the EMC regulations. Within its technical committee structure, the IEC has two committees dedicated full time to EMC: the CISPR (International Special Committee on Radio Interference), which publishes standards related to the limits and methods of measurements for radiated and conducted interference; and the TC 77, whose publications deal with EMC between equipments, specifying electromagnetic environments, measurement techniques, emissions, immunity, etc. Although these international regulations are not mandatory, they serve as a foundation to the regulations created by other international organizations, national commisions, and manufaturers [60].

Within the United States the FCC (Federal Communications Commission) is in charge of the regulations of radio and wire communication, which include the control of the interference in such communications. The FCC rules and regulations are cointained in [61], and cover any device with timing pulses frequencies of at least 10 kHz. The devices are classified into two classes: 1) class A, for devices used in comercial, industrial, or bussines environment; and 2)

class B, for residential devices. The FCC regulations are compulsory, and it is illegal to market a device in the United States if it doesn't comply with them.

In Europe, the CENELEC (European Committee for Electrotechnical Standardization) is the European body in charge of producing EMC standards fo use with the European EMC directive, and it is made up of the national committees of each country. Once the CENELEC has produced an EMC European standard, all the member countries are required to implement identical national standards. The European EMC directive [75] harmonises the "generic standards" (for both emissions and immunity) as well as the "product standards". The generic standards such as EN61000-6-1...4 [62][63][64][65] are responsible to set out limits and test procedures, while the product standards such as EN61800-3 (for adjustable-speed electrical PDS) [66] etc. cover specific types of products.

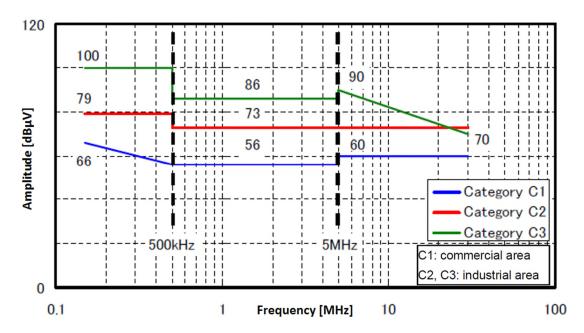

The pulse frequencies of the PDS are often chosen in the range around (usually lower than) 10 kHz. For the harmonics in the frequency range of 150 kHz to 30 MHz, the product standard specifies different limits of the conducted emissions. To determine which of the limits are to be complied with, the standard defines two kinds of application environments of the PDS: On one side, the "first environment" is defined for the equipment which is connected directly to the lowvoltage (less than 1000 V of AC RMS voltage, defined by IEC) power grid without an intermediate transformer, supplying power to buildings that are used for residential purposes (houses, apartments, shops or offices in residential buildings). In the first environment, the standard is further classified in Category 1 (C1) and Category 2 (C2), these two categories can be distinguished from each other by the concept "restricted / unrestricted distribution". That means, when the PDS is operated by a person without any EMC knowledge, the situation belongs to C1; when the person has EMC knowledge, it belongs then to C2. On the other side, the "second environment" is defined as the environment that contains all other facilities that are not directly connected to a low-voltage power grid which supplies power to buildings used for residential purposes. In the second environment, the standard classifies the Category 3 (C3) for the PDS with the rated voltage of less than 1000 V. In Fig. 2-8, the limits of the conducted EMI for the categories C1, C2 and C3 (here only for the PDS with a current consumption of less than 100 A) are presented.

From another point of view, in the generic standars EN61000-6-1...4, the specifications divides the applications into "industrial area" and "commercial area". By the conducted EMI emission limits, there are correlations between the product- and the generic-standards: The category C1 of the product standard correlates to the commercial area that is defined by the generic standard, while the categories C2 and C3 correlate to the industrial area.

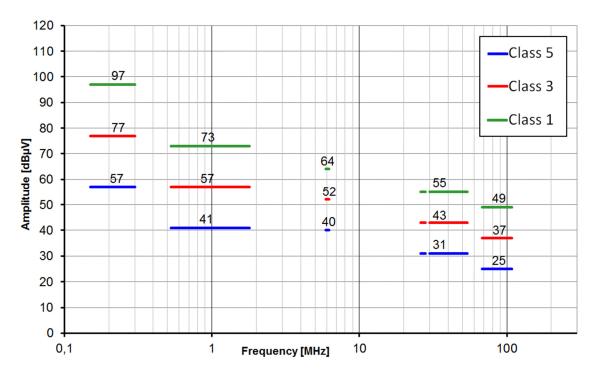

Fig. 2-8: Limits (Quasi-Peak values) of conducted EMI in product- and generic-standards

As for the automotive applications, the existing standard CISPR 25 [67] from IEC is considered to be the most relevant normative reference. The CISPR 25 applies to any electronic / electrical component intended for use in vehicles, trailers and devices; it contains limits and procedures for the measurement of radio disturbances in the frequency range of 150 kHz to 2.5 GHz. The limits are intended to provide protection for receivers installed in a vehicle from disturbances produced by components / modules in the same vehicle. The receiver types to be protected are, for example, broadcast receivers (sound and television), land mobile radio, radio telephone, amateur, citizens' radio, satellite navigation (GPS etc.) and Bluetooth. Since the mounting location, vehicle body construction and harness design can affect the coupling of radio disturbances to the on-board radio, the CISPR 25 defines multiple limit levels. For example, the Quasi-Peak levels of conducted EMI for components / modules in the vehicle are defined in 5 classes in the frequency range of 150 kHz to 108 MHz (Fig. 2-9 and Table 1). The level class to be used (as a function of frequency band) shall be agreed upon between the vehicle manufacturer and the component supplier (meaning the power module manufacturer in this dissertation). The diverse discontinuous frequency bands that are defined in Table 1 are not applicable to all regions or countries of the world. For economic reasons, the vehicle manufacturer must be free to identify what frequency bands are applicable in the countries in which a vehicle will be marketed and which radio services are likely to be used in that vehicle [67].

Fig. 2-9: Limits (Quasi-Peak values, voltage method) of conducted EMI in standard CISPR 25 for components / modules in automotive application

Table 1: Quasi-Peak levels (voltage method) of conducted EMI for components / modules of the vehicle in standard CISPR 25

| Service / Frequenc |             | Quasi-Peak levels [dBµV] |         |         |         |         |

|--------------------|-------------|--------------------------|---------|---------|---------|---------|

| Band               | [MHz]       | Class 1                  | Class 2 | Class 3 | Class 4 | Class 5 |

| Broa               | Broadcast   |                          |         |         |         |         |

| LW                 | 0.15 - 0.30 | 97                       | 87      | 77      | 67      | 57      |

| MW                 | 0.53 -1.8   | 73                       | 65      | 57      | 49      | 41      |

| SW                 | 5.9 - 6.2   | 64                       | 58      | 52      | 46      | 40      |

| FM                 | 76 -108     | 49                       | 43      | 37      | 31      | 25      |

| Mobile Services    |             |                          | l       | l       | l       | l       |

| СВ                 | 26 -28      | 55                       | 49      | 43      | 37      | 31      |

| VHF                | 30 -54      | 55                       | 49      | 43      | 37      | 31      |

| VHF                | 68 -87      | 49                       | 43      | 37      | 31      | 25      |

LW: Long wave, MW: Medium wave, SW: Short wave (amplitude modulation, AM)

FM: Frequency modulation

**CB**: Cell Broadcast

VHF: Very high frequency

The measurement results of high-frequency EMI are often influenced by many external factors during the course of the measurement. In order to prevent or minimize such influences, the

measurement setups for the conducted and radiated EMI are normalized respectively by the standard CISPR16-1 for industrial application as well as the standard CISPR 25 for automotive application. Principally the measurement setups for the both kinds of applications don't quite differ from each other. Usually the following components are essential parts of the conducted EMI test bench:

- Power supply

- Artificial network (LISN)

- DUT (power semiconductor module in this dissertation)

- Load (real motor or simulator)

- Power supply lines

- Load wires / cables

- Ground plane

- Shielded enclosure

- Measuring instrument (Scanning receiver or spectrum analyzer)

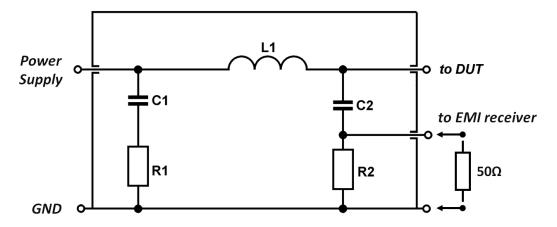

The specifics of the components, such as their materials, their locations, their parameters and the test procedures etc. are respectively defined in each standard depending on the industrial or automotive applications. The conducted emission measurement generally includes two kinds of methods: the voltage method and the current probe method. Although it can characterize the emissions on single leads only, yet the voltage measurement is the most frequently used method because of its simple and normalized setup. For both of the measurement methods, to be able to correlate the measured data between different measurements sites, the impedance seen by the DUT, and over which these measurements are made, has to be stabilized from site to site. Therefore, a normative AN (Artificial network) which is also named as the LISN (Line Impedance Stabilization Network) is needed. The use of the LISN during the conducted EMI measurements serves mainly two purposes: 1) to prevent external conducted noise (from the power lines) from contaminating the measurements and, 2) to present constant impedance between the grounding and the power line, making sure that the measurements are reproducible [15]. The schematic representation of a single phased LISN is shown in Fig. 2-10. The presence of the capacitor  $C_1$  and the inductor  $L_1$  is to divert the external noise from the power supply, preventing them from contaminating the EMI measurement results over the tested frequency ranges. The 50  $\Omega$ resistor represents the input impedance of the measuring instrument. The capacitor  $C_2$  is constructed to prevent any DC voltage from overloading the measuring instrument. The resistors  $R_1$  and  $R_2$  serve to discharge the capacitors  $C_1$  and  $C_2$  in case the 50  $\Omega$  resistor is removed. The values of these passive components in the LISNs for industrial and automotive applications are compared to each other in Table 2.

Table 2: Comparison of the parameters in LISN for industrial / automotive applications

| Application field | L <sub>1</sub> [µH] | C₁ [µF] | C <sub>2</sub> [µF] | R <sub>1</sub> [Ω] | $R_2[\Omega]$ |

|-------------------|---------------------|---------|---------------------|--------------------|---------------|

| Industrial        | 50                  | 8       | 0.47                | 5                  | 1000          |

| Automotive        | 5                   | 1       | 0.1                 | 0                  | 1000          |

Fig. 2-10: Schematic of single phase LISN in the drive system for EMI measurement

# 2.2. Switching behavior of semiconductors and its characterization

Since the switching operation of the power semiconductors is regarded as the main cause of the EMI, the switching characteristics of the IGBT and diode shall be considered more specifically. In this chapter, the relevant basic knowledge about the dynamic performances of the semiconductors within the power module are indroduced. After that, the manner of the measurements in laboratory, whereby the dynamic characteristics of the semiconductors in power module can be investigated, are presented. These measurement methods and setups will be used to characterize the switching performance of the EMI-optimized power modules in the chapter 6 of this dissertation.

## 2.2.1. IGBTs and diodes in power modules

The discussion regarding the switching behavior of the power semiconductor chips (IGBTs and diodes) without considering their packaging is less meaningful, because the construction and connection of the chips can bring additional parasitic components, which significantly impact or limit the power semiconductors' dynamic and static performances.

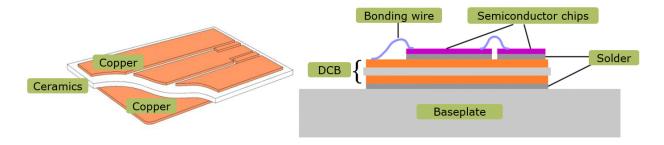

In order to fulfill the demands of various output power densities, the power semiconductor chips are usually assembled in discrete form, disc-cell or module. Nowadays most modules are built up through various combinations of soldering and bonding processes. The realization of these processes can be summarized in Fig. 2-11: The top and bottom sides of each silicon chip provide contacts with a thick metal layer of approximately 5 µm. Bonding wires are applied on the top side of the chip, while the chip's bottom side is connected to the substrate via solder joints. The substrates differ essentially in their production processes. Typically used substrates are Direct Copper Bonded (DCB) or Active Metal Brazed (AMB). In these, copper or aluminum are combined with aluminum oxide or aluminum nitride ceramic to form a layer structure. The

top side copper is then patterned by an etching processes to generate different tracks. The benefit of the ceramic and copper substrate is that its thermal expansion coefficient is close to that of silicon. Due to the ceramic insulation layer, the power module has two major advantages: Firstly, this insulating layer separates the voltage level inside the module from the heat sink (basic insulation) and thus allows the trouble-free installation of several modules on the same heat sink; Secondly, this isolation allows the operation of components at different potential levels (functional insulation) [72]. The DCB substrate used in this dissertation is usually made of aluminum oxide ( $Al_2O_3$ ) with approximately 300  $\mu$ m thick copper layers on both sides. The contacting of the semiconductor chip top side is realized by bonding processes with aluminum wire, recently also copper wire.

The advantages of the power modules are, on the one hand, the possibility of structuring the upper copper layer of the DCB as a conductive pattern, which enables the electrically isolated construction of a complete circuit (e.g., three-phase inverter) in one module; on the other hand, the simplicity of the installation.

Fig. 2-11: Constructions of DCB (left) and power module without frame (right) in sectional view

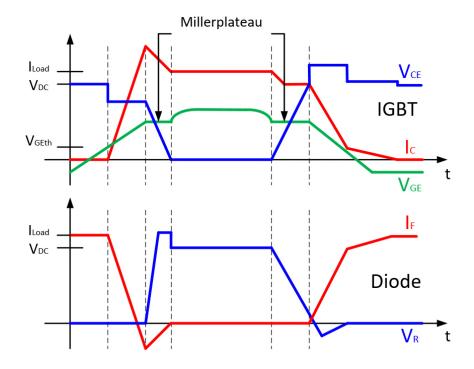

Fig. 2-12: Switching-on and -off performances of IGBT and diode in power module

The IGBT is controlled by the gate voltage  $V_{GE}$ . If the gate voltage is negative, it stays in the off state. As soon as the gate voltage reaches the threshold voltage  $V_{GEth}$ , the IGBT becomes conductive and the load current can commute from the diode to the IGBT. In addition to the load current, the IGBT takes over the reverse recovery current of the free-wheeling diode and carries a current peak during the turn on process. According to the law of induction by  $\Delta V_{CE} = L \cdot \frac{dI_C}{dt}$ , the current change rate  $dI_C/dt$  causes a voltage drop at the module's parasitic inductances in the commutation cell. This voltage drop counteracts the driving DC-link voltage  $V_{DC}$  and is visible as a voltage dip in the collector-emitter voltage  $V_{CE}$ .

After reaching the reverse recovery current peak, the diode can take over the reverse bias and the reverse current starts to drop. Only then the voltage on the IGBT can decrease. The decreasing voltage  $dV_{CE}/dt$  causes an additional current in the parasitic capacitances of the commutation cell, which overlaps with the IGBT current  $I_C$ . During this time, the drop of the diode's reverse current with a certain rate of  $dI_F/dt$  can lead to an overvoltage which burdens the diode itself (as well as its parallel IGBT at the same side of the half-bridge). At the same time, the gate-collector capacitance (Miller capacitance) must be recharged. The gate-emitter voltage  $V_{GE}$  remains constant during the recharging period and thereby forms the so-called Miller plateau. When the diode has taken over the entire blocking voltage, the gate voltage rises to its final value and the static turn-on state is reached.

By receiving the turn-off command, the gate voltage drops to the Miller plateau. During the plateau, the IGBT takes over the voltage drop again. Meanwhile, the voltage across the diode decreases. According to the equation  $\Delta I_C = C \cdot \frac{dV_{CE}}{dt},$  the changing voltage  $dV_{CE}/dt$  causes an additional current in the parasitic capacitances of the commutation cell, that is visible as a current dip in the collector-emitter current  $I_C.$

The diode can start to take over the current only when the entire blocking voltage drops across the IGBT. The commutation current's steepness  $dI_{\rm C}/dt$  has an opposite sign during turn-off and turn-on. Therefore, the blocking voltage across the IGBT is increased due to the additionally induced voltage caused by the stray inductances of the whole commutation path. Thus, an overvoltage peak is formed during the turn-off process. After that, the minority carriers in the IGBT must be removed from the device, which causes a collector current tail.

As mentioned before, the impact of the semiconductor chips' construction and connection in the power module are critical. The switching curves  $V_{CE}$  (resp.  $V_R$ ) and  $I_C$  (resp.  $I_F$ ) can deviate strongly from ideal trapezoidal curves due to parasitic elements. If the dimension of the parasitic elements in the power module is changed, the reshaped switching characteristics are directly visible. For example, at the same operation point, reducing the stray inductances in the commutation cell can lead to proportional decrease in the voltage drop during the IGBT turn-on as well as reduced overvoltage peak during the IGBT turn-off [18]. Furthermore, from the emission point of view, stray inductances are of particular importance by investigating the EMI of inverters, since, given certain values in combination with parasitic capacitances from the power module or from the drive system, they can lead to resonance in the HV circuit and excite oscillations.

## 2.2.2. Characterizing the switching behavior through double-pulse measurements

In order to characterize the switching behavior of the IGBT and diode, proper dynamic measurements in the laboratory are necessary. The preferred measurement method in this dissertation is called the "double-pulse test". This measurement method is widely used by the power semiconductor manufacturers because of its simplicity and reproducibility during its implementation.

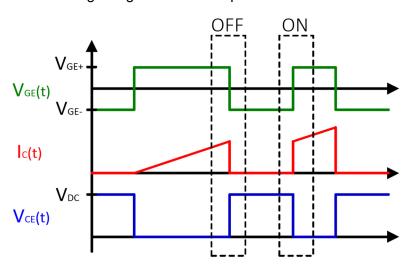

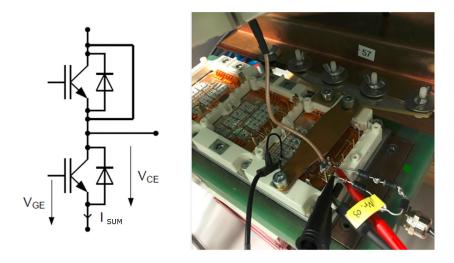

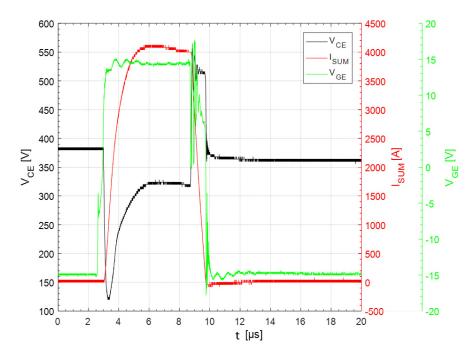

The double-pulse test can be described as follows: During the test, the IGBT in one side of the power module's half-bridge is turned on and off twice. Fig. 2-13 shows the typical voltages ( $V_{CE}$  and  $V_{GE}$ ) as well as current ( $I_C$ ) profiles during the measurement. The first pulse allows the load current flowing through the switching IGBT to build an initial status. This pulse must be long enough in order to ensure that the IGBT reaches a steady state in conducting direction, and be as long as needed (in the test usually between 50  $\mu$ s to 100  $\mu$ s), so that the needed magnitude of the current flow is reached, before the IGBT turns off. After that, the IGBT must remain in off state until the free-wheeling diode has reached steady state of conduction (in the test usually set to 100  $\mu$ s). Then, the IGBT is turned on once again for a short while (approx. 15  $\mu$ s) until the voltage  $V_{CE}$  has decreased to the collector-emitter saturation voltage  $V_{CE}$  before finally turning off, by which point the whole test process is completed. From the characterization point of view, the IGBT switching off behavior is recoded at the end of the first pulse; the IGBT switching on as well as the reverse recovery behavior of the free-wheeling diode are recoded at the beginning of the second pulse.

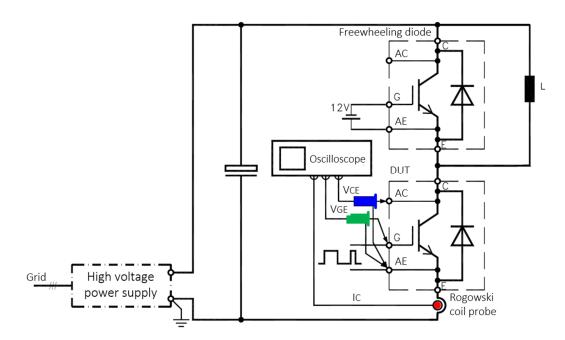

Fig. 2-13: The course of the double-pulse test

To realize the double-pulse characterization, the power module with the semiconductors inside as the DUT is basically operated under a buck converter mode. That means, the IGBT in one side of the half-bridge is connected in series with an external inductive load (mostly a coil) and controlled by the gate signals to switch on / off, while the diode in the other side of the half-bridge is working as a free-wheeling diode to conduct the load current intermittently. The schematic for the measurements of the IGBT (from low side of the half-bridge) and of its free-wheeling diode (from high side of the half-bridge) is presented in Fig. 2-14. Depending on the connected position of the oscilloscope's grounding, a transformer between the grid and the

power supply may be necessary to separate the tested high voltage system from the general GND.

For the trials in this work, the inductive load is connected between the positive node of the DClink and the AC output (also possible between DC- and AC node, depending on which side of the semiconductor is measured), resulting in a parallel connection with the HS IGBT which stays constantly in OFF state. The LS IGBT is connected and controlled by an Infineon® driver board. This so called "EV-driver" can generate an output voltage from the positive rail to GND by 0.6 V to 28 V. From the negative rail to GND, it can be 0 V to -20 V. Furthermore, the driver has 8 switching stages in which 8 R<sub>qon</sub>s and 8 R<sub>qoff</sub>s can be switched separately from each other. The driver itself is supplied with a DC voltage of 15 V. The switching pulse comes via a fiber optic cable and is converted by the driver into an electrical signal to output. Thus there is no microcontroller on the driver itself that generates the switching pulse. To select the switching stage and the voltage, an Ethernet connection to a PC is required. The driver configuration is then done via a Labview-tool. The capacitor used for the DC-link is the EPCOS® film capacitor B25655J4507K, with a capacitance of 500  $\mu$ F, ESR of approx. 1 m $\Omega$ , and ESL of approx. 15 nH [71]. The power module and the capacitor bus bar are connected through flat terminals with screws, resulting in short paths with low stay inductances of less than 10 nH per line. According to [73], minimum parasitic inductance allows improving power semiconductors towards lower losses. The oscilloscope WaveRunner HRO 66Zi from LeCrov<sup>®</sup> is used to record the switching curves; it has a maximum sampling rate of 2 GHz, and a sensitivity of up to 1 mV/div. The vertical resolution of the oscilloscope is 12 bits. The currents flowing through the IGBT or the diode are measured with a PEM® CWT Rogowski coil probe (CWT15), which is mounted around the terminals connecting the DC-link with the power module. The high voltage drops V<sub>CE</sub> or V<sub>R</sub> are measured with the PMK<sup>®</sup> high voltage probe PHV 1000 with the probe factor of 100. The gate-emitter voltage V<sub>GE</sub> of the active IGBT is usually measured with the Tektronix® passive probe P6139B. If the auxiliary emitters (AE) used for the V<sub>CE</sub> and V<sub>GE</sub> measurements are from different sides of the half-bridge, a TESTEC differential probe (TT-SI 9110) can be used for either V<sub>CE</sub> or V<sub>GE</sub> measurement (This unusual situation is not covered in the schematic below).

Fig. 2-14: Schematic for IGBT measurement in the double-pulse test

### 3. Investigations about the EMI source

The use of fast switching devices (such as IGBTs) in PWM inverters causes EMI problems in the drive system or grid respectively. The generated high voltage slew rate dv/dt and high current slew rate di/dt during the switching processes have been established as the main source of EMI in electrical applications [9].To characterize the EMI of the inverter, it is meaningful to focus on the device switching effects at first.

### 3.1. FFT analysis of unideal switching edge

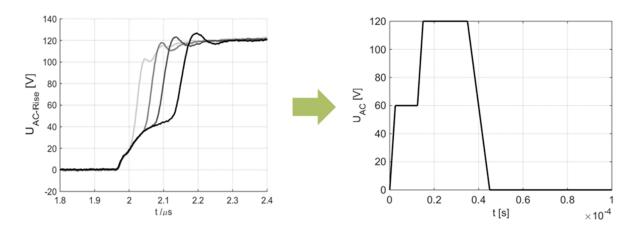

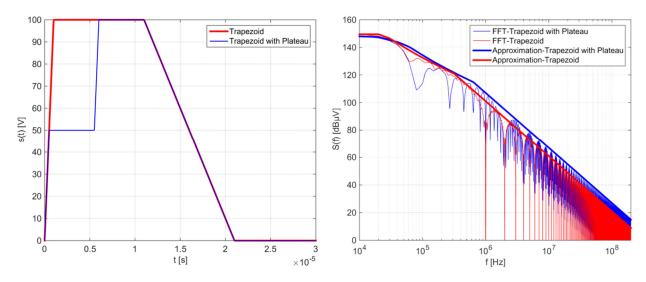

As explained in chapter 2.1.1, the switching frequency related output voltages of power modules as well as their commutation currents are approximated as pulse-shaped with simplex rising and falling edges. In this dissertation, for better approaching of the output voltage, the researched object is a deformed trapezoidal pulse in time-domain, by which an extra plateau with constant amplitude is added into the rising edge of the trapezoid. The reason for choosing this kind of pulse to study can be explained as follows: During the operation of the inverter respectively the power module, the shape of the output voltage (U<sub>AC</sub>) is changing. The steepness of the rising edges is affected by the load current and the stray inductance of the construction. The origin for this effect will be discussed and explained in detail in 3.2.2. In this sub-chapter we only focus on the mathematical discussion of the influences in frequency-domain that are brought by the deformation of the trapezoidal pulse. As presented in Fig. 3-1, the deformed rising edge of the output voltage can be approximated by a constant rising edge with an inserted plateau. The approximated rising edge can be combined with a falling edge with constant steepness and form a deformed trapezoidal pulse, which is called "trapezoid with plateau" in this dissertation.

Fig. 3-1: Measured deformed rising edges of the output voltage in power module (left) and the approximation by the "trapezoid with plateau" (right)

In order to compare the spectrums of the trapezoidal pulses with and without plateau, the maximum spectrum limits of the trapezoid with plateau shall be found out first. The trapezoid with plateau in time-domain can be taken apart into two standard trapezoids with half of the amplitude. As shown in Fig. 3-2, the target shape in black with a plateau of  $t_p$  and amplitude of A can be considered to consist of the 1<sup>st</sup> trapezoid in green combined with the 2<sup>nd</sup> trapezoid in red. The two sub-trapezoids with different average durations are superimposed on each other. To simplify the calculation, the durations of the rising and falling edges for each sub-trapezoid are set to be  $\frac{R}{2}$  and  $\frac{F}{2}$ , respectively half of the target shape. The segmented functions of each shape are defined in Table 3. The parameters are normalized and marked with an apostrophe: t' = t/T, M' = M/T, R' = R/T and F' = F/T and  $t'_p = t_p/T$ .

Fig. 3-2: Decomposition and parameterization of the target trapezoid with plateau (black) into two sub-trapezoids (green and red) in staggered position

Table 3: Defining the segmented functions of the trapezoid with plateau and its two subtrapezoids

|                                                    | Function s(t')                                                   |                                                                  |                                                        |  |

|----------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------|--|

| Section                                            | Trapezoid with plateau                                           | 1 <sup>st</sup> sub-trapezoid                                    | 2 <sup>nd</sup> sub-trapezoid                          |  |

| 0 ≤ t' < t' <sub>1</sub>                           | $\frac{A}{R'}t'$                                                 | $\frac{A}{R'}t'$                                                 | 0                                                      |  |

| ${t'}_1 \le t' < {t'}_2$                           | $\frac{A}{2}$                                                    |                                                                  |                                                        |  |

| ${t'}_2 \le t' < {t'}_3$                           | $\frac{A}{R'}(t'-t'_p)$                                          | $\frac{A}{2}$                                                    | $\frac{A}{R'} \left( t' - t'_p - \frac{R'}{2} \right)$ |  |

| ${t'}_3 \le t' < {t'}_4$                           | A                                                                | 2                                                                | $\frac{A}{2}$                                          |  |

| ${t'}_4 \le t' < {t'}_5$                           | $\frac{A}{F'}\left(\frac{R'}{2} + M' + \frac{F'}{2} - t'\right)$ |                                                                  | $\frac{A}{F'} \left( \frac{R'}{2} + M' - t' \right)$   |  |

| ${t'}_5 \le t' < {t'}_6$                           | F'\2 2 1                                                         | $\frac{A}{F'}\left(\frac{R'}{2} + M' + \frac{F'}{2} - t'\right)$ | 0                                                      |  |

| ${\mathsf t'}_6 \le {\mathsf t'} < {\mathsf t'}_7$ | 0                                                                | 0                                                                |                                                        |  |

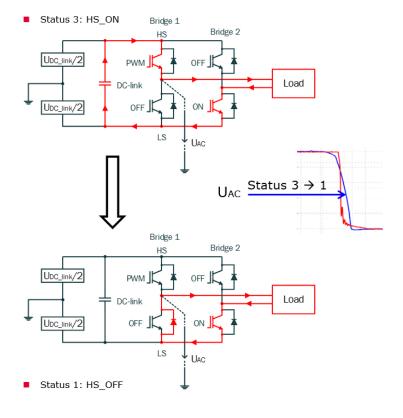

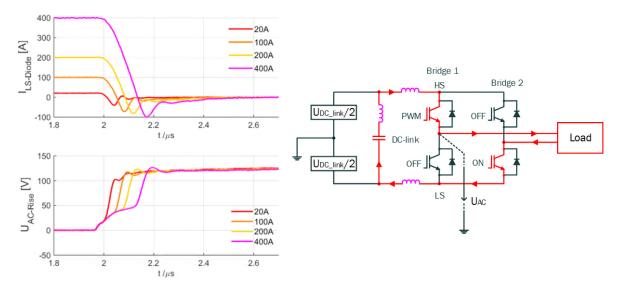

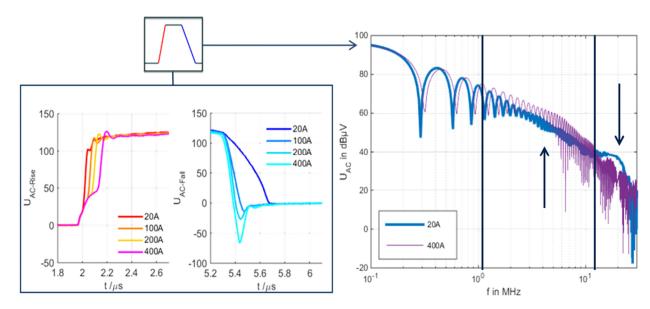

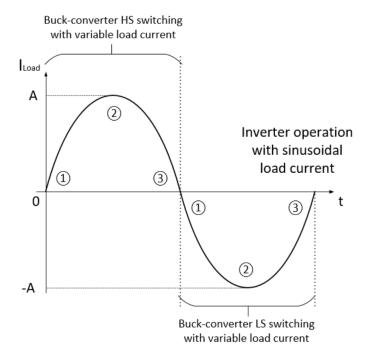

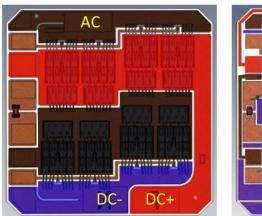

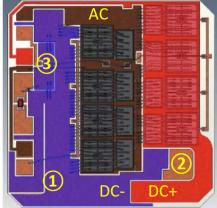

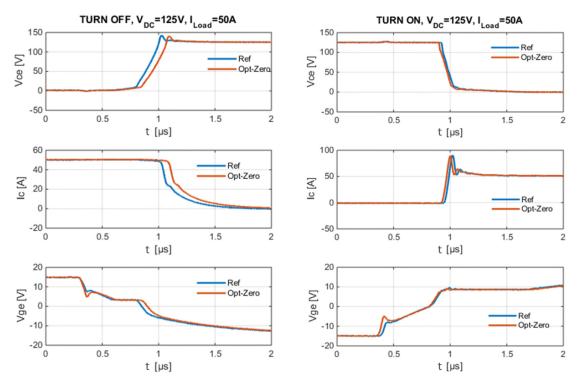

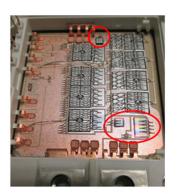

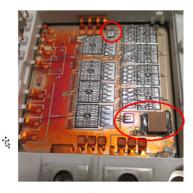

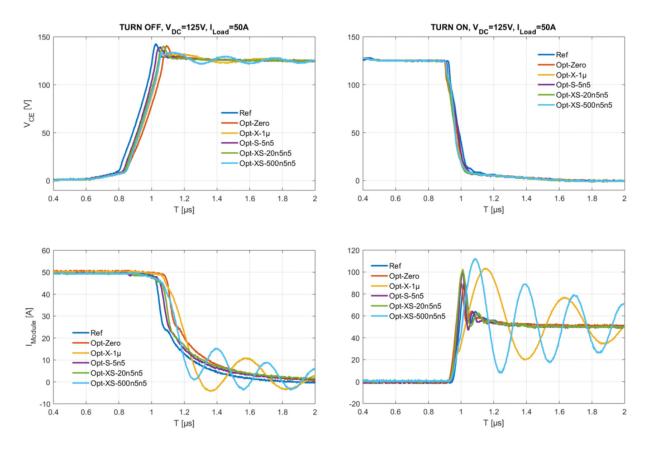

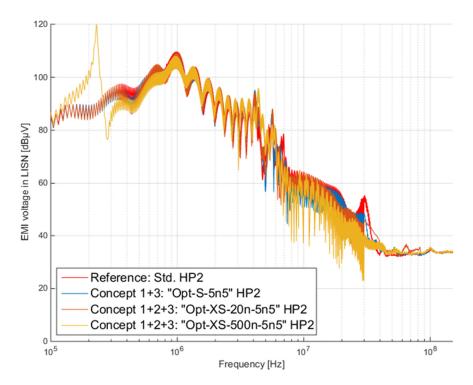

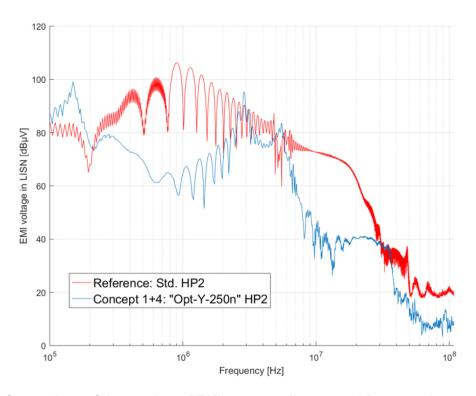

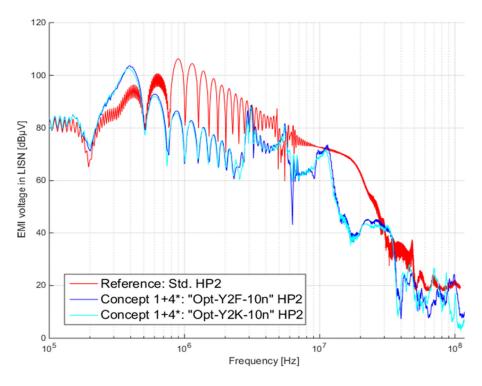

By using the methods that are presented in [5] for the approximation of the spectrums, the segmented functions in frequency-domain of the approximated spectrums can be listed in Table 4, compared to that of a standard trapezoidal pulse. For frequencies in the range of the switching frequency  $\frac{1}{T}$  (respectively  $f < f_{k1}$  in Fig. 2-4), the spectrum can be determined by the value of the switching frequency, by assuming that k = 1 (k = fT) in the equation (2-3). In this first section of the function S(f) in Table 4, the spectrums remain approximately constant, the steepness of the approximated lines correspond to 0 dB / decade. Compared to a standard trapezoid for reference, the average durations of the two sub-trapezoids' pulses are different.